PRELIMINARY

IRDA

S3C6400X RISC MICROPROCESSOR

38-12

Preliminary product information describe products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

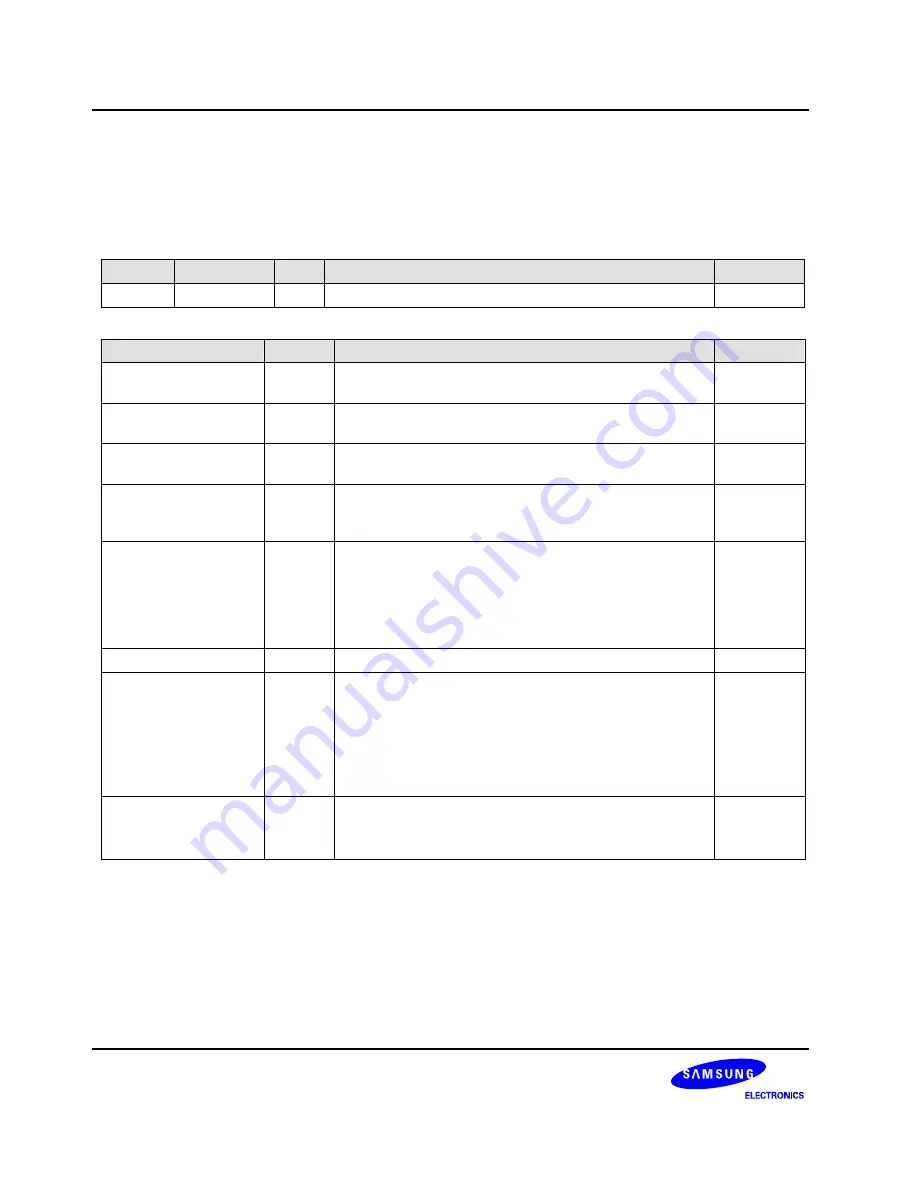

SPECIAL FUNCTION REGISTERS

IRDA CONTROL REGISTER(IRDA_CNT)

Register

Address

R/W

Description

Reset Value

IrDA _CNT 0x7F00_7000

R/W

IrDA Control Register

0x00

IrDA _CNT

Bit

Description

Initial State

TX enable

[7]

TX enabled. Bit 7 must be set to ‘1’ to enable data

transmission in MIR/FIR Ir modes.

0

RX enable

[6]

RX enabled. Bit 6 must be set to ‘1’ to enable data receive

in all MIR/FIR Ir modes.

0

Core loop

[5]

Core loop for software debugging. The IRRX port

connects directly to the IRTX internally.

0

MIR half mode

[4]

MIR half mode. When bit 4 is set to a ‘1’, the operating

speed in the MIR mode changes from 1.152 Mbps to

0.576 Mbps.

0

Send IR pulse

[3]

Send 1.6-us IR pulse. When the IrDA_MDR[3] bit equals

to a ‘1’ and the CPU writes a ‘1’ to this bit, the transmitting

interface device sends a 1.6-us IR pulse at the end of the

frame. Bit 3 is cleared automatically by the transmitting

interface device at the end of 1.6-us IR pulse data

transmission.

0

Reserved [2]

Reserved

0

Frame abort

[1]

Frame abort. The CPU can intentionally abort data

transmission of a frame by writing a ‘1’ to bit 1. Neither the

end flag nor the CRC bits are appended to the frame. The

receiver will find the frame with the abort pattern in the

MIR mode and a PHY-error in the FIR mode. The CPU

must reset the TX FIFO and reset this bit by writing a ‘0’ to

bit ‘1’ before next frame can be transmitted.

0

SD/BW

[0]

This signal controls IrDA_SDBW output signal.

It is used for controlling mode (shutdown, band width) of

IrDA transceiver.

0