3–110

Altera Corporation

Stratix II GX Device Handbook, Volume 2

October 2007

Channel and Clock Multiplier Unit (CMU) PLL Reconfiguration

1

The main TXPLL corresponds to the TX PLL configuration set in

the

General

tab of the ALT2GXB MegaWizard and the alternate

TXPLL corresponds to the

Reconfig Alt PLL

tab.

Channel and CMU PLL Reconfiguration Duration

The dynamic reconfig controller takes the following number of reconfig

clock cycles to write the contents in the MIF:

■

Words 0 to 27 - approximately 260 clock cycles per word

■

Words 28 to 37 - approximately 521 clock cycles per word

Reset Recommendations

Altera recommends that you follow a proper reset sequence during and

after CMU PLL reconfiguration.

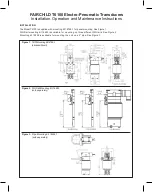

Figure 3–55

shows the recommended

reset sequence.

Figure 3–55. Reset Sequence During and After CMU PLL Reconfiguration (1 > 2 > 3 > 4 > 5)

As shown in

Figure 3–55

, assert the

tx_digitalreset

,

rx_digitalreset

and

rx_analogreset

when you initiate the CMU

PLL reconfiguration MIF writes. After the dynamic reconfiguration

control completes the CMU PLL reconfiguration, it asserts the

channel_reconfig_done

signal. After the

channel_reconfig_done

signal goes high, wait for

pll_locked

and

pll_locked_alt

(if you are using the alternate PLL) to go high (as

channel_reconfig_done

tx_digitalreset

rx_analogreset

rx_digitalreset

rx_freqlocked

3

3

4

5

Output Status Signals

1

2

pll_locked_alt

pll_locked_final

pll_locked

T = 4us

Содержание Stratix II GX

Страница 640: ...4 244 Altera Corporation Stratix II GX Device Handbook Volume 2 October 2007 Document Revision History ...

Страница 642: ...4 246 Altera Corporation Stratix II GX Device Handbook Volume 2 October 2007 Document Revision History ...

Страница 672: ...6 14 Altera Corporation Stratix II GX Device Handbook Volume 2 October 2007 Document Revision History ...