CAN modules

UM0404

DocID13284 Rev 2

Note:

With a CAN module clock of 8 MHz, the reset value of 0x2301 configures the C-CAN for a

bitrate of 500 Kbit/s. The registers are only writable if bits

CCE

and

Init

in the CAN Control

Register are set.

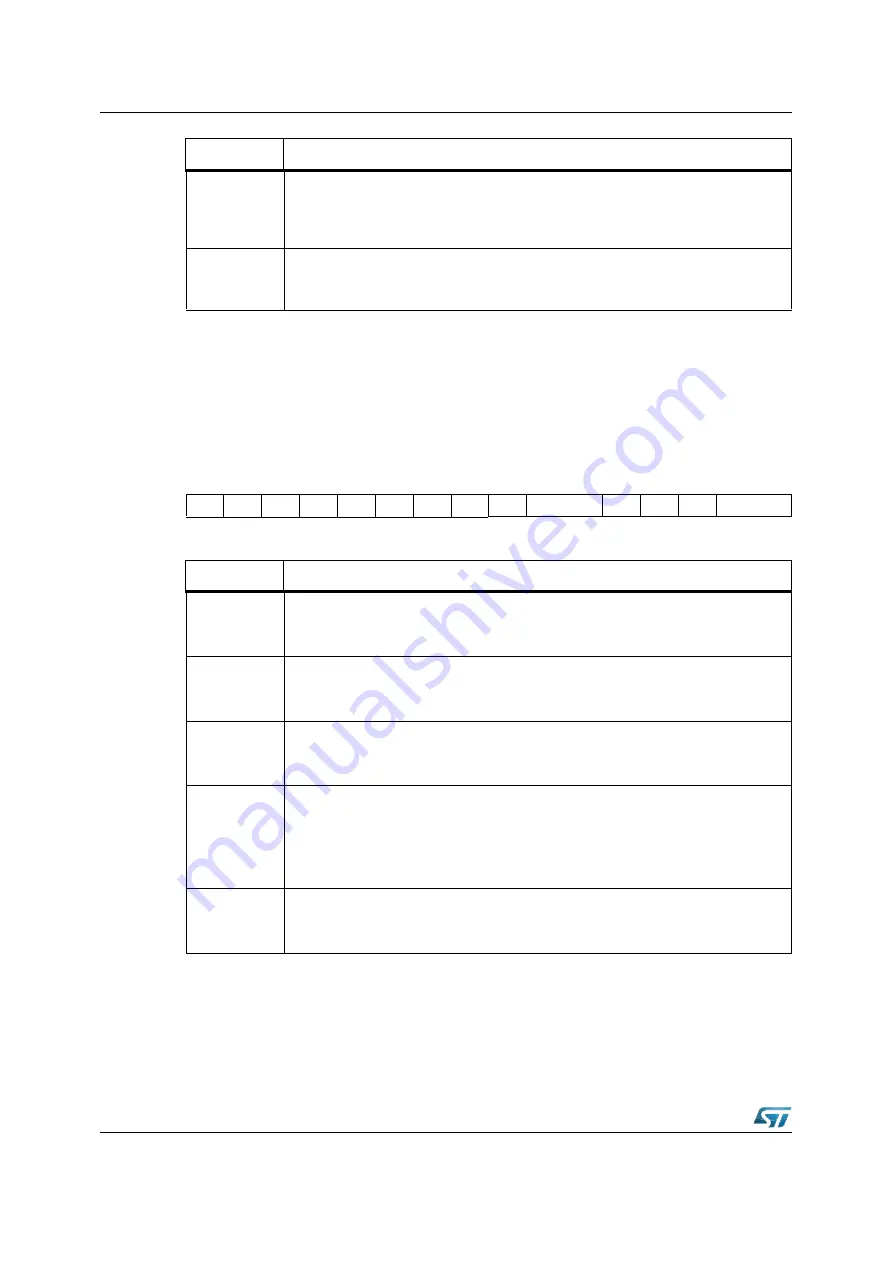

Test register

CAN1TR (EF0Ah)

XBUS

Reset Value: 00x0h

CAN2TR (EE0Ah)

XBUS

Reset Value: 00x0h

Write access to the Test Register is enabled by setting bit

Test

in the CAN Control Register.

The different test functions may be combined, but

Tx(1:0)

≠

“00” disturbs message transfer.

TSeg1

Time segment before the sample point

Valid values for TSeg1 are 01h-0Fh (1…15). The actual interpretation by the

hardware of this value is such that one more than the value programmed here is

used.

TSeg2

Time segment after the sample point

Valid values for TSeg2 are 0h-7h (0…7). The actual interpretation by the hardware

of this value is such that one more than the value programmed here is used.

Bit

Function

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

-

-

-

-

-

-

-

-

Rx

Tx(1:0)

LBack Silent Basic

-

RW

RW

RW

RW

RW

Bit

Function

Basic

Basic Mode

’0’: Basic Mode disabled.

’1’: IF1 Registers used as Tx Buffer, IF2 Registers used as Rx Buffer.

Silent

Silent Mode

’0’: Normal operation.

’1’: The module is in Silent Mode.

LBack

Loop Back Mode

’0’: Loop Back Mode is disabled.

’1’: Loop Back Mode is enabled.

Tx(1:0)

CAN_TxD pin control

’00’: Reset value, CAN_TxD is controlled by the CAN Core.

’01’: Sample Point can be monitored at CAN_TxD pin.

’10’: CAN_TxD pin drives a dominant (‘0’) value.

’11’: CAN_TxD pin drives a recessive (‘1’) value.

Rx

Actual CAN_RxD pin value monitor

’0’: The CAN bus is dominant (CAN_RxD = ‘0’).

’1’: The CAN bus is recessive (CAN_RxD = ‘1’).