CAN modules

UM0404

DocID13284 Rev 2

21.8.1

Hardware reset description

After hardware reset, the registers of the C-CAN hold the values described in

Additionally the

busoff

state is reset and the output

CAN_TxD

is set to

recessive

(HIGH).

The value 0x0001 (

Init

= ‘1’) in the CAN Control Register enables the software initialization.

The C-CAN does not influence the CAN bus until the CPU resets

Init

to ‘0’.

The data stored in the Message RAM is not affected by a hardware reset. After Power-On,

the contents of the Message RAM is undefined.

21.8.2 CAN

protocol related registers

These registers are related to the CAN protocol controller in the CAN Core. They control the

operating modes and the configuration of the CAN bit timing and provide status information.

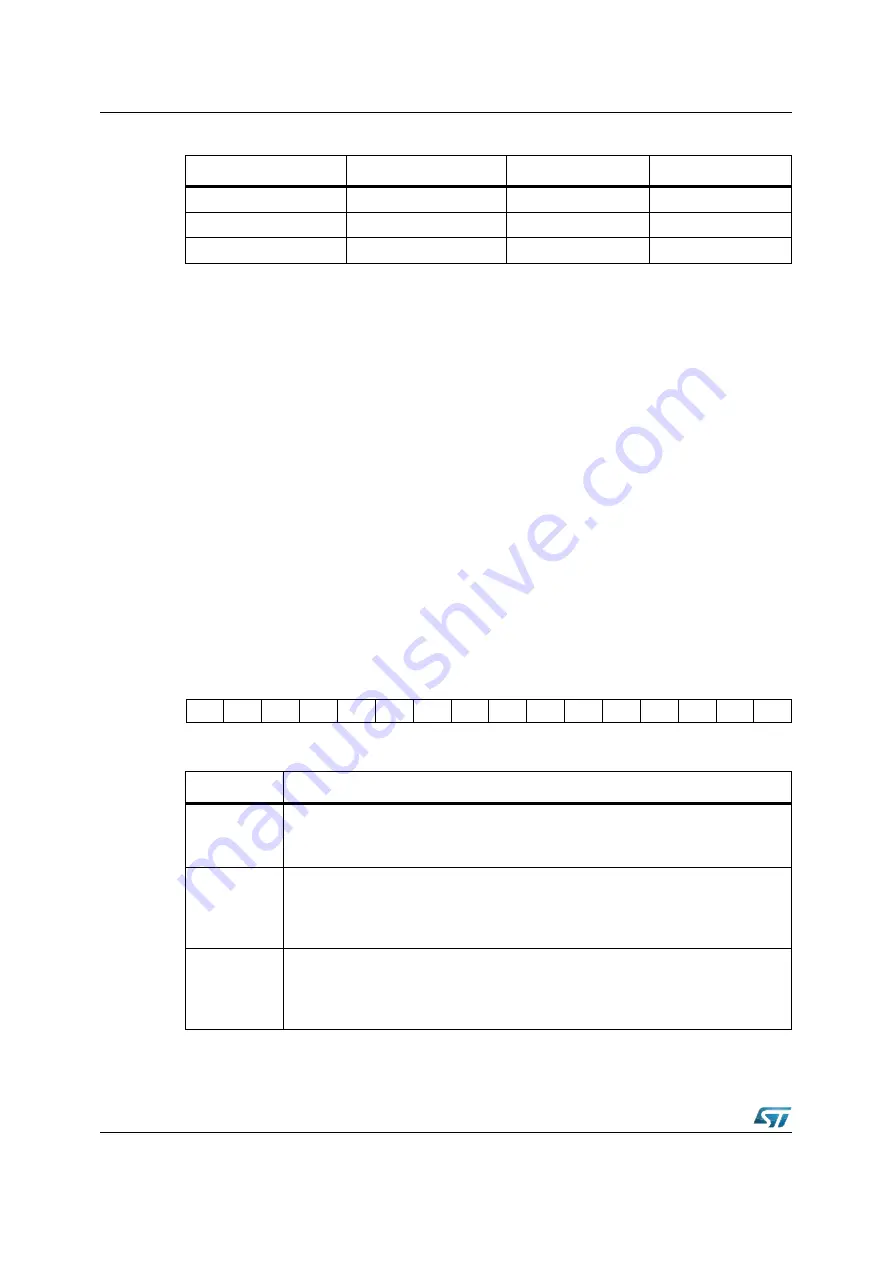

CAN control register

CAN1CR (EF00h)

XBUS

Reset Value: 0001h

CAN2CR (EE00h)

XBUS

Reset Value: 0001h

CAN Base + 0xB0

Message Valid 1

0x0000

read only

CAN Base + 0xB2

Message Valid 2

0x0000

read only

CAN Base + 0xB4 - 0xBE — reserved

—

1.

r signifies the actual value of the CAN_RxD pin.

2.

Reserved bits are read as ‘0’ except for IFx Mask 2 Register where they are read as ‘1’.

3.

The two sets of Message Interface Registers - IF1 and IF2 - have identical functions.

Table 60. C-CAN register memory space summary

Address

Name

Reset value

Note

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

-

-

-

-

-

-

-

-

Test CCE DAR

-

EIE

SIE

IE

Init

RW

RW

RW

RW

RW

RW

RW

Bit

Function

Init

Initialization

’0’: Normal Operation.

’1’: Initialization is started.

IE

Module Interrupt Enable

’0’: Disabled - Module Interrupt

IRQ_B

is always HIGH.

’1’: Enabled - Interrupts will set

IRQ_B

to LOW.

IRQ_B

remains LOW until all

pending interrupts are processed.

SIE

Status Change Interrupt Enable

’0’: Disabled - No Status Change Interrupt will be generated.

’1’: Enabled - An interrupt will be generated when a message transfer is successfully

completed or a CAN bus error is detected.