CAN modules

UM0404

DocID13284 Rev 2

Note:

CAN Parallel mode is effective only if both CAN1 and CAN2 are enabled through the setting

of bits CAN1EN and CAN2EN in XPERCON register. If CAN1 is disabled, CAN2 remains on

P4.4/P4.7 even if bit CANPAR is set.

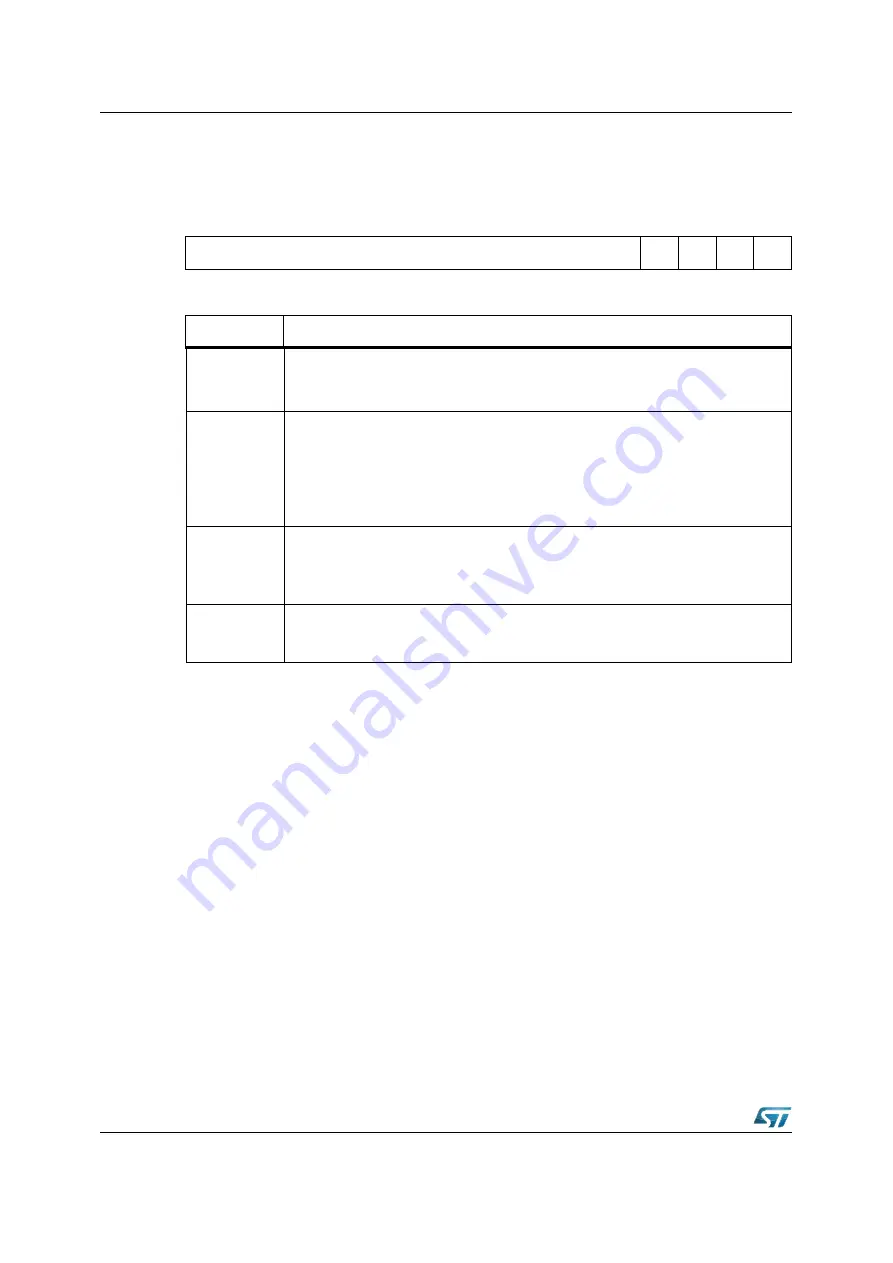

XMISC (EB46h)

XBUS

Reset Value: 0000h

21.3.1 Configuration examples

The following figures show different configuration examples, where the two CAN controllers

of the ST10F276 are working on the same CAN bus or on different CAN busses.

Wired-or connections to a CAN bus use open drain outputs as described above. A wired-or

structure can be used for on-board data exchange between two or more controller devices

via one signal line. As no CAN transceiver is used in this case, the maximum wire length is

very limited (<< 1 m) and noise conditions must be considered.

Finally, when one bus only is interfaced, the parallel mode for the two on-chip CAN modules

allows to double the buffer capability, and to save two pins for other functionalities. The

receive lines are internally tied together, while the transmit lines from the two modules are

logically ANDed on the single pin: this is done to assign to the pin the active value driven by

one of the two (for CAN protocol logic level ‘1’ is the recessive state, so the non-transmitting

CAN module, allows the other to drive the pin).

Note that after reset, the port pin are in high impedance, so an external pull-up is always

needed to grant the recessive level on Tx lines.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

–

VREG

OFF

CAN

CK2

CAN

PAR

ADC

MUX

–

RW

RW

RW

RW

Bit

Function

ADCMUX

Port1L ADC Channels Enable

‘0’: Analog inputs on port P5.y can be converted (default configuration)

‘1’: Analog inputs on port P1.z can be converted. Only 8 channels can be managed

CANPAR

CAN Parallel Mode Selection

‘0’: CAN2 is mapped on P4.4/P4.7, while CAN1 is mapped on P4.5/P4.6

‘1’: CAN1 and CAN2 are mapped in parallel on P4.5/P4.6. This is effective only if

both CAN1 and CAN2 are enabled through setting of bits CAN1EN and CAN2EN in

XPERCON register. If CAN1 is disabled, CAN2 remains on P4.4/P4.7 even if bit

CANPAR is set.

CANCK2

CAN Clock divider by 2 disable

‘0’: Clock provided to CAN modules is CPU clock divided by 2 (mandatory when

f

CPU

is higher than 40 MHz)

‘1’: Clock provided to CAN modules is directly CPU clock

VREGOFF

Main Voltage Regulator disable for Power Down mode

‘0’: Default value after reset and when Power Down is not used.

‘1’: On-chip Main Regulator is turned off when Power Down mode is entered.