GR716-DS-UM, May 2019, Version 1.29

456

www.cobham.com/gaisler

GR716

45.8.2

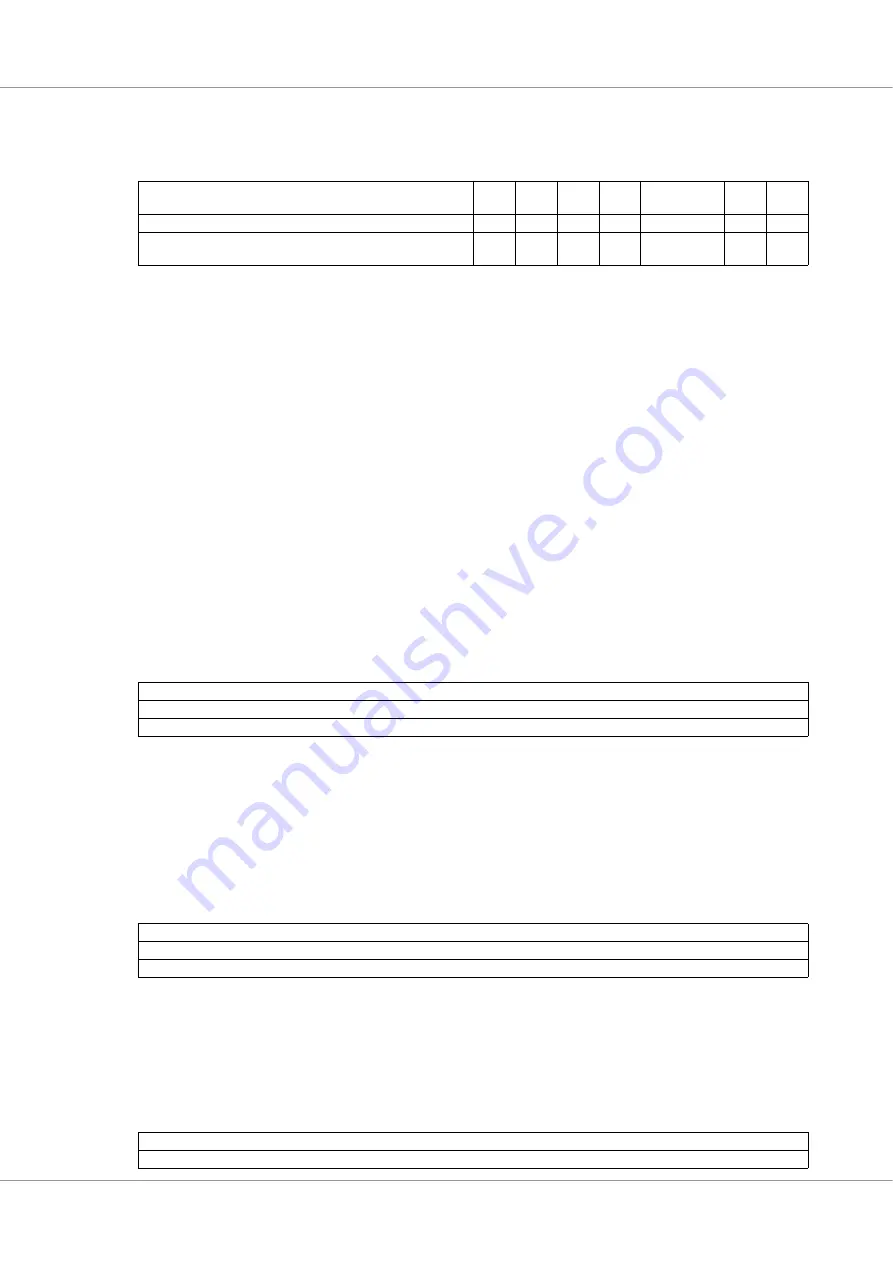

Table 612.

0x04 - STAT - Status register

Status Register

45.8.3 Transmit Register

Table 613.

0x08 - TDATA - Transmit register

45.8.4 Nominal Receive Register

Table 614.

0x0C - NRDATA - Nominal receive register

45.8.5 Redundant Receive Register

31

8

7

6

5

4

3

2

1

0

RESERVED

ATR

ATN

SAR

SIC

R

RR

RN

0

0

1

0

0

0

0

0

r

r

r

r

r

r

r

r

31 : 3

RESERVED

7

Active transmission in redundant port (ATR) - This bit provides the status of the redundant transmis-

sion port. Set based on the incoming activate and deactivate commands (active ‘1’ else ‘0’). Valid

only for SPI protocol 2 implementation.

6

Active transmission in nominal port (ATN) - This bit provides the status of the nominal transmission

port. Set based on the incoming activate and deactivate commands (active ‘1’ else ‘0’). Valid only

for SPI protocol 2 implementation.

5

Status address error (SAR) - This bit gets set to ‘1’ when an AMBA write or read access resulted in a

error. A valid new command clears this status bit. Valid only for SPI protocol 2 implementation.

4

Status illegal command (SIC) - This bit gets set to ‘1’ when an illegal command is received. A valid

new command clears this status bit. Valid only for SPI protocol 2 implementation.

3 : 2

RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

1

Received data redundant (RR) - This bit gets set to ‘1’ each time a data is received in the redundant

port. The bit gets set to ‘0’ when the Redundant receive register is read.

0

Received data nominal (RN) - This bit gets set to ‘1’ each time a data is received in the nominal port.

The bit gets set to ‘0’ when the Nominal receive register is read.

31

0

TDATA

0

rw

31 : 0

Transmit data (TDATA) - The written data is transferred to the master device when appropriate con-

ditions for CS and SCK are satisfied. The word to transmit should be written with its least significant

bit at bit 0. Also note that only the number of bits need to be transferred from this register should

match the word length register (WLEN). Valid only for SPI protocol 0 and 1.

31

0

NRDATA

0

r

31 : 0

Nominal Receive data (NRDATA) - This register contains received data from the nominal port. Valid

only for SPI protocol 0 and 1.

Table 615.

0x10 - RRDATA - Redundant receive register

31

0

RRDATA

0