69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69r

lq62d-f714peg4 * Memec (Headquar

ters) - Unique

T

ech, Insight, Impact * UNDER ND

A# 12101050

MAR

VELL CONFIDENTIAL - UNA

UTHORIZED DISTRIB

UTION OR USE STRICTL

Y PR

OHIBITED

Services Power Management Unit

Copyright © 12/13/06 Marvell

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

December 13, 2006

Document Classification: Proprietary Information

Page 191

Not approved by Document Control. For review only.

8.6.5

Watchdog Reset

The watchdog reset is invoked when software fails to properly prevent the watchdog time-out event from

occurring for that timer. The watchdog reset from within the PXA300 processor is the watchdog reset and is

output to the entire processor architecture and causes a reset the same as if a hardware reset had been asserted

except for those modules listed in

.

8.6.5.1

Invoking Watchdog Reset

Watchdog reset is invoked when the WME bit in the “OS Timer Watchdog Match Enable register (OWER)” in

the timer module, and the “OS Timer Match register 3 (OSMR3)” matches the OS timer counter. The OS counter

for channel 3 only increments in S0/D0/C0, S0/D0/C1 and S0/D0CS modes. A watchdog reset cannot occur in

S0/D1/C2, S0/D2/C2, S2/D3/C4 or S3/D4/C4.

When this event occurs, watchdog reset is entered regardless of the previous mode. When watchdog reset is

invoked, the entire processor reset is asserted except to the units as shown in

, resetting the services

unit, application subsystem, and the pad unit. Additionally, all pins assume their reset states, including SYS_EN

which is negated.

The sequence for watchdog reset is:

1. The PXA300 processor OS timer asserts watchdog reset (OSMR3 matches the OS timer counter.)

2. The PXA300 processor OS timer watchdog reset is reset automatically as a result of propagation of the

internal application-subsystem reset state, and the services unit, and the pad unit are reset.

3. The reset is de-asserted.

The hardware reset sequence is executed by the services unit, and normal boot-up sequencing begins for the

application subsystem, with all units starting with their predefined reset state. The application core software must

examine the “Application Subsystem Reset Status register (ARSR)” to determine that the reset source was a

watchdog reset.

8.6.6

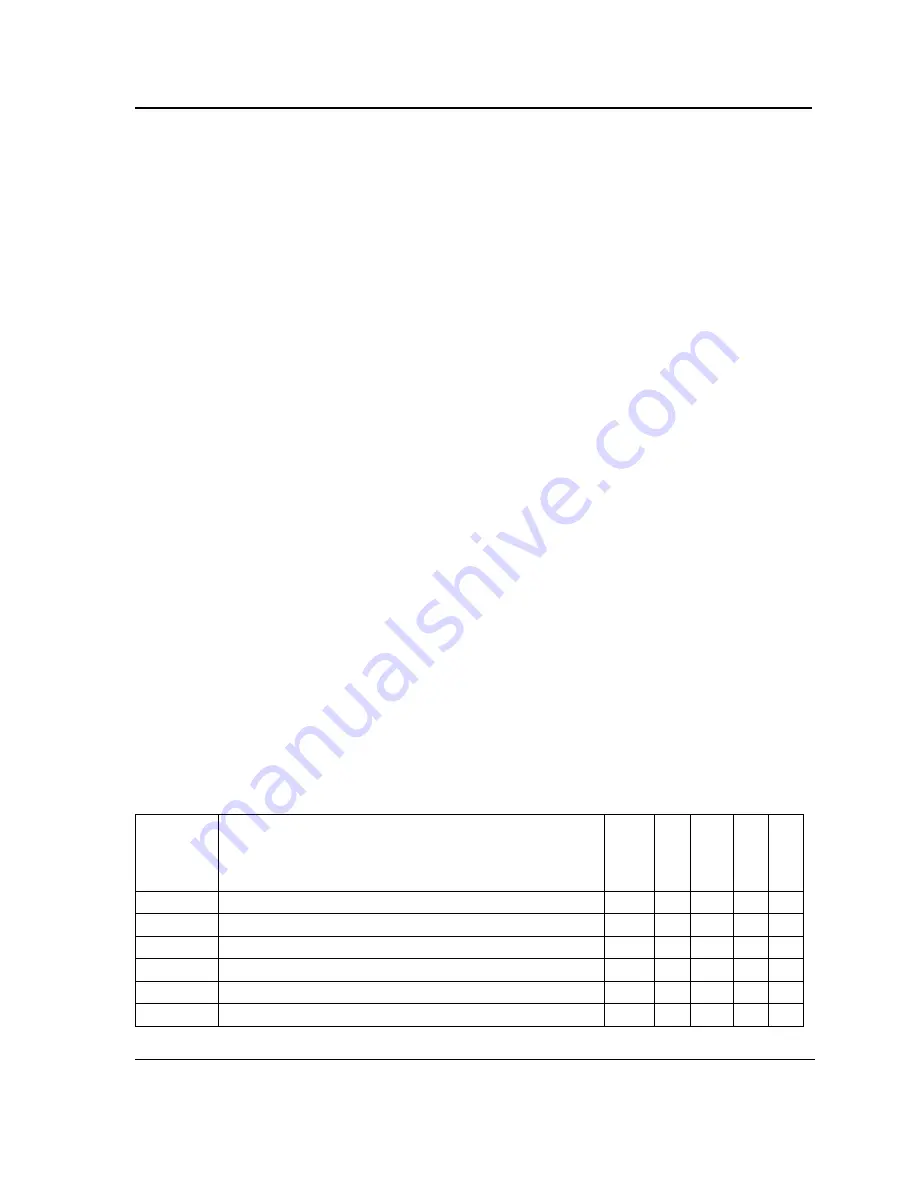

Summary of Module Reset Sensitivity

The registers and functions of most modules take their default, or reset, value when entering any of the five reset

modes. The exceptions to this are listed in

Table 8-2. Summary of Module Reset Functions (Sheet 1 of 2)

Services

Unit Module

Register Name or Function

L

o

w-

P

o

we

r

S

tate E

x

it

GP

IO

Gl

o

b

a

l

W

a

tc

hdo

g

Ha

rd

w

a

re

P

o

we

r-

On

PWR_I

2

C

All registers and functions including PVCR

x

†

x

x

x

RTC

RTTR

x

x

RTC

Other registers and functions

x

x

x

MPMU

JCONR, All bits in PMCR except BIE and BIS

x

†

x

x

x

MPMU

PSR, PSPR, PCFR, PWER, PWSR, PECR, and BIE and BIS in PMCR

x

x

x

MPMU

DCSR

x