Rev. 1.0, 09/02, page 151 of 568

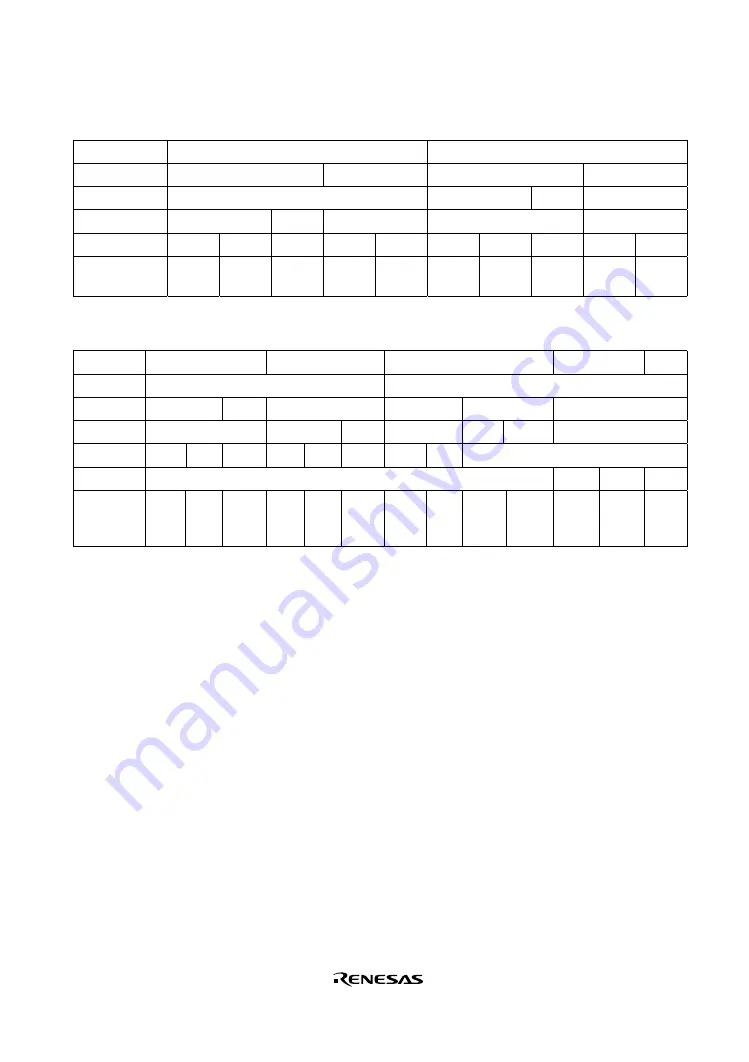

Table 9.44 PC1 Pin Function

MSS 0

1

BIDE 0 1 0 1

RE

0

1

TE 0

1

PC1DDR 0

1

0 1 0 1

0 1

Pin function

PC1

input

PC1

output

SSI0

output

PC1

input

PC1

output

PC1

input

PC1

output

SSI0

input

PC1

input

PC1

output

Table 9.45 PC 0Pin Function

MSS

0 1

0

1

BIDE

0 1

RE

0 1

0

1

0

TE

0

1

0

0

1 1

PC0DDR

0 1

0 1

0 1

0 1

Pin

function

PC0

in-

put

PC0

out-

put

SSO0

in-

put

PC0

in-

put

PC0

out-

put

SSO0

out-

put

PC0

in-

put

PC0

out-

put

SSO0

input

Setting

pro-

hibited

SSO0

out-

put

SSO0

Hi-z

SSO0

out-

put

Содержание H8S/2627

Страница 22: ...Rev 1 0 09 02 page xx of xxxvi Index 565 ...

Страница 30: ...Rev 1 0 09 02 page xxviii of xxxiv ...

Страница 36: ...Rev 1 0 09 02 page xxxiv of xxxiv Table 23 9 Flash Memory Characteristics 561 ...

Страница 82: ...Rev 1 0 09 02 page 46 of 568 ...

Страница 88: ...Rev 1 0 09 02 page 52 of 568 ...

Страница 98: ...Rev 1 0 09 02 page 62 of 568 ...

Страница 156: ...Rev 1 0 09 02 page 120 of 568 ...

Страница 390: ...Rev 1 0 09 02 page 354 of 568 ...

Страница 480: ...Rev 1 0 09 02 page 444 of 568 ...

Страница 512: ...Rev 1 0 09 02 page 476 of 568 ...

Страница 527: ...Rev 1 0 09 02 page 491 of 568 21 8 5 Writing to MSTPCR MSTPCR should only be written to by the CPU ...

Страница 528: ...Rev 1 0 09 02 page 492 of 568 ...

Страница 580: ...Rev 1 0 09 02 page 544 of 568 ...