Performance Evaluation

51

CG635 Synthesized Clock Generator

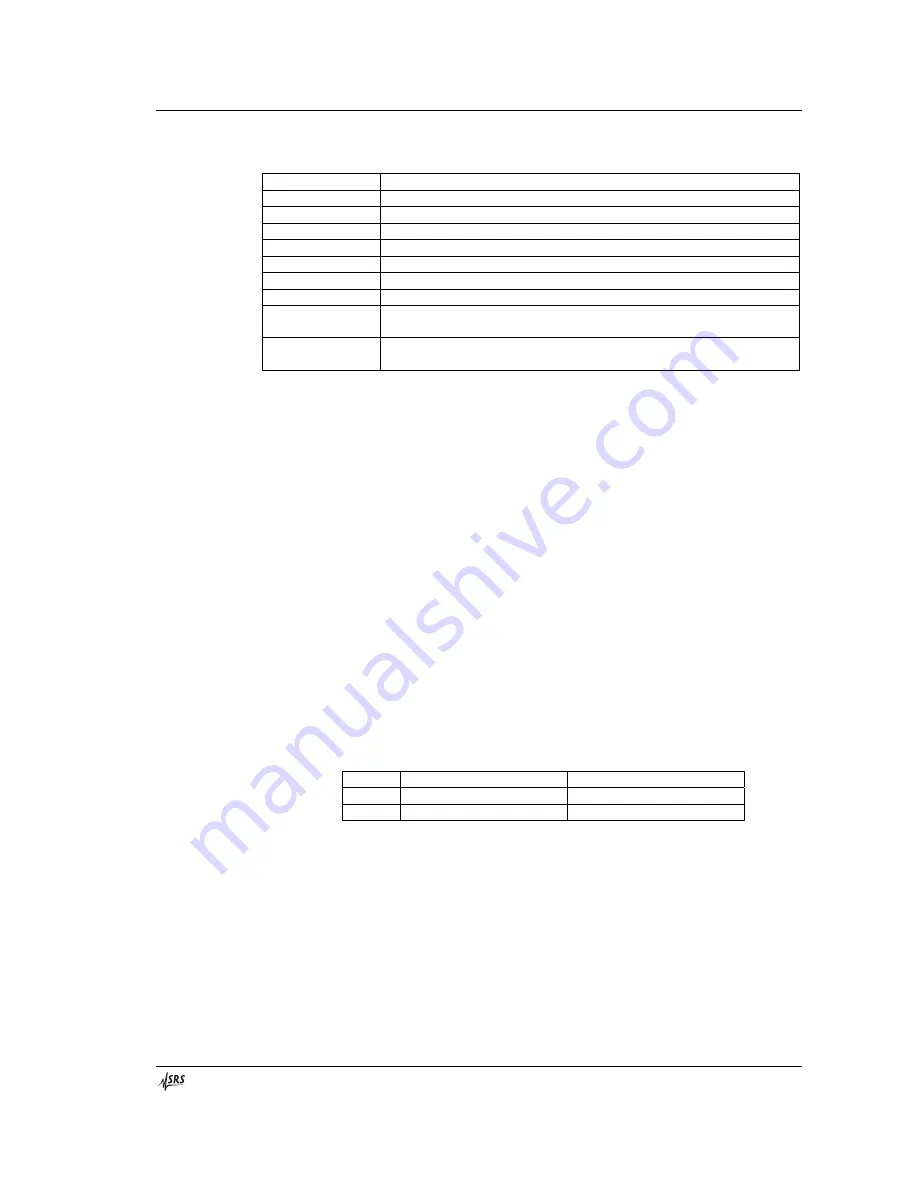

Table 21: HP 54120A digitizing scope setup for Q/Q

¯ timing

Parameter Setting

Trigger

0.0V level, positive slope, HF sens. off, HF reject off

Trig. Slope

Positive

Volts/div

20 mV for channel 2 and 3

Offset

0.0 V for channel 2 and 3

Time/div 50

ps

Delay

Reference at center, value adjusted to center transition in the display

Display

Channels 2 and 3, averaged with count of 4

V Markers

Marker 1: –30 mV

Marker 2: +30 mV

T Markers

Start Marker: adjusted to time where Q/Q

¯ waveform crosses V Marker 1

Stop Marker: adjusted to time where Q/Q

¯ waveform crosses V Marker 2

The scope delay will have to be adjusted manually until the transitions from the 200 MHz

output are located. Once the delay is properly adjusted to center the transition on the

display, the complementary transition can be readily obtained by adding 2.5 ns to the

delay.

Measure the rise-time by adjusting the T Markers so that the Start Marker is located at the

point where the waveform crosses V Marker 1 and the Stop Marker is located at the point

where the waveform crosses V Marker 2. Record the

¨

t of the markers as the rise time of

the given waveform.

Measure the fall-time by adjusting the T Markers so that the Start Marker is located at the

point where the waveform crosses V Marker 2 and the Stop Marker is located at the point

where the waveform crosses V Marker 1. Record the

¨

t of the markers as the fall time of

the given waveform.

The rise-time of Q and the fall-time of Q

¯ can be measured at one delay setting. The rise-

time of Q

¯ and the fall-time of Q can be measured at a reference delay that is 2.5 ns later.

The measured transition times should meet the specifications given in Table 22.

Table 22: Maximum allowed transition times for Q/Q

¯ outputs

Output Meas. (Rising, Falling) ps

Max. ( Rising, Falling) ps

Q

(100,

100)

Q

¯

(100,

100)

CMOS Timing Measurements

For the CMOS output timing measurements, configure the HP 54120A digitizing scope

as in Table 23.