141

Chapter 3

CPU Functions

User’s Manual U16580EE3V1UD00

(3)

System status register (PHS)

The PHS register is an 8-bit register to which the PRERR flag showing the generation of

protection errors is assigned.

If a write operation to a specific register has not been executed in the correct sequence including

the access to the command register (PRCMD), the write operation to the intended register is not

executed, a protection error is generated and the PRERR flag is set to 1. The value of this register

becomes “00H” by RESET input.

This register can be read/written in 8-bit and 1-bit units.

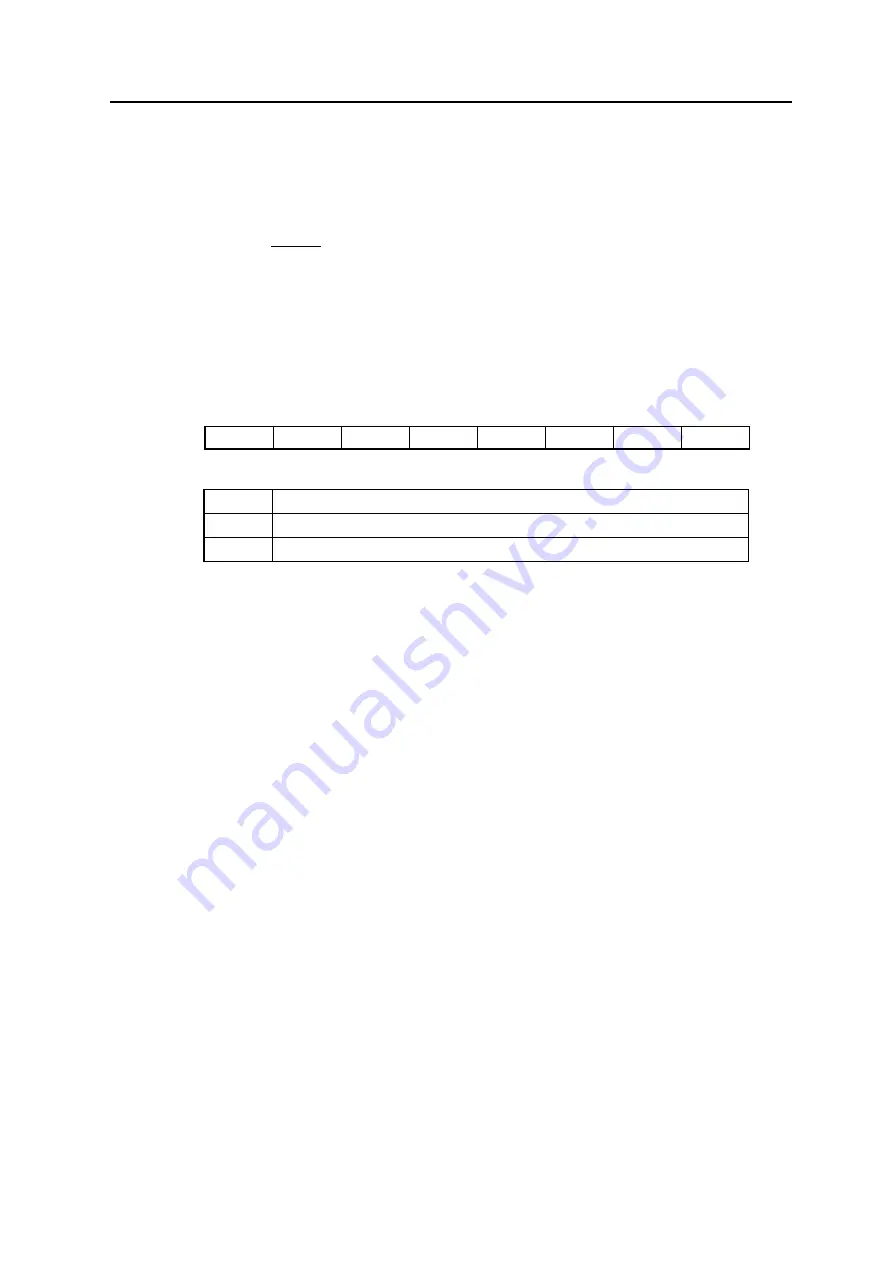

Figure 3-26:

System Status Register Format PHS

The PRERR flag operates under the following conditions.

(a) Setting condition (PRERR flag = 1)

•

When a write operation is not performed on the PRCMD register and an operation to write a

specific register is performed (when <4> in the example

3.4.8

(1) Setting data to specific

registers

is executed without <3>).

•

If a write operation (including a bit manipulation instruction) is performed on an on-chip

peripheral I/O register other than a specific register after a write operation to the PRCMD

register (when <4> in the example

3.4.8

(1) Setting data to specific registers

is not performed

for a specific register).

Remark:

Even if an on-chip peripheral I/O register is read (including a bit manipulation instruction)

between writing the PRCMD register and writing a specific register (such as an access to

the internal RAM), the PRERR flag is not set, and data can be written to the special register.

(b) Clearing condition (PREER flag = 0)

•

When 0 is written to the PRERR flag of the PHS register.

•

When system reset is executed.

Cautions: 1. If 0 is written to the PRERR bit of the PHS register (that is not a specific register)

immediately following write to the PRCMD register, the PRERR bit becomes 0

(write priority).

2. If data is written to the PRCMD register (that is not a specific registers)

immediately following write to the PRCMD register, the PRERR bit becomes 1.

After reset:

00H

R/W

Address:

FFFFF802H

7

6

5

4

3

2

1

0

PHS

0

0

0

0

0

0

0

PRERR

PRERR

Detection of Protection Error

0

Protection error did not occur

1

Protection error occurred

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......