IDT Configuration Registers

PES24N3A User Manual

9 - 32

April 10, 2008

Notes

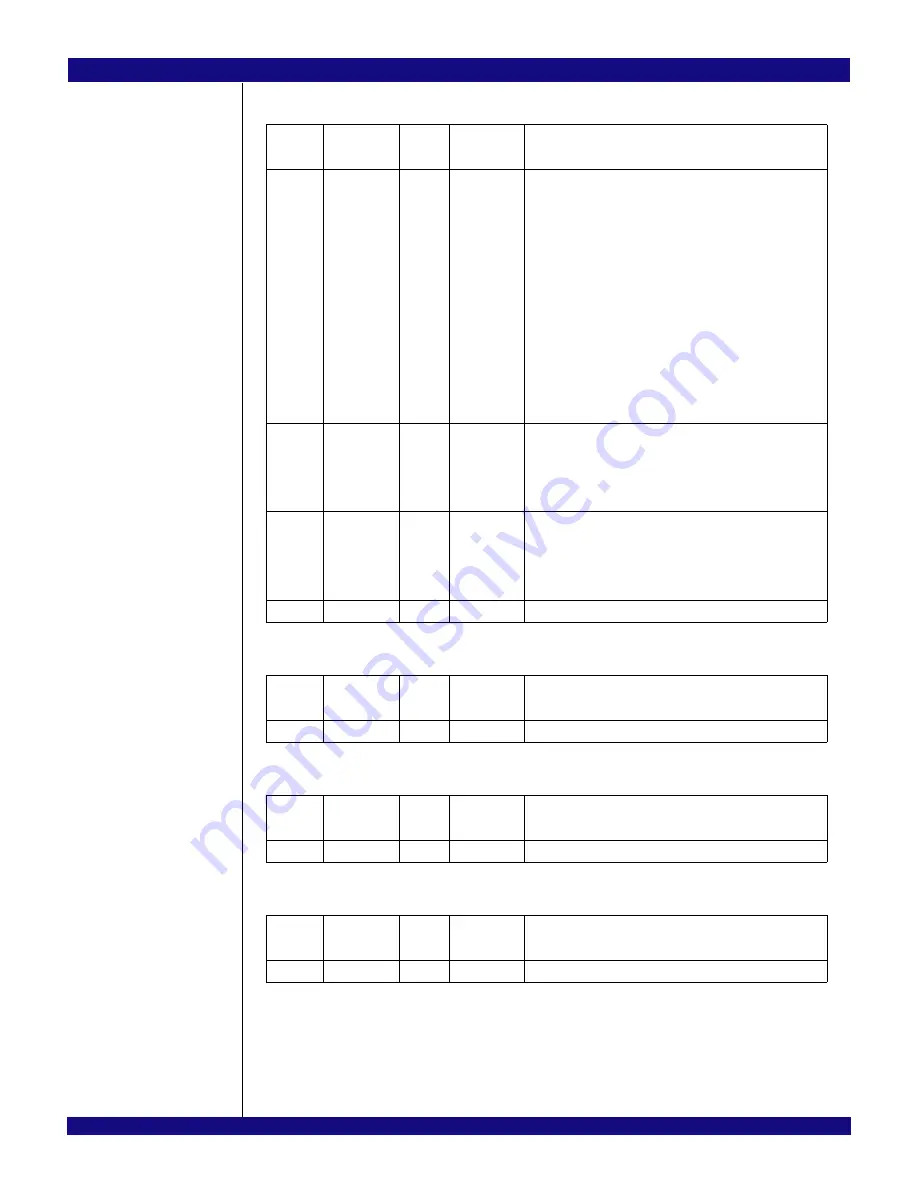

PCIELCTL2 - PCI Express Link Control 2 (0x070)

PCIELSTS2 - PCI Express Link Status 2 (0x072)

PCIESCAP2 - PCI Express Slot Capabilities 2 (0x074)

PCIESCTL2 - PCI Express Slot Control 2 (0x078)

Bit

Field

Field

Name

Type

Default

Value

Description

3:0

TLS

RW

0x0

Target Link Speed

. For downstream ports, this field sets an

upper limit on the link operational speed by restricting the

values advertised by the upstream component in its training

sequences.

For both upstream and downstream ports, this field is used

to set the target compliance mode speed when software is

using the ECOMP bit in this register to force a link into com-

pliance mode.

The PES24N3A only supports 2.5 Gbps operation. Setting

this field to an unsupported value produces undefined

results.

1 -(gen1) 2.5 Gbps

2 -(gen2) 5 Gbps

others-reserved

This field is read-only zero in PCIe 1.1 mode.

4

ECOMP

RW

0x0

Sticky

Enter Compliance

. Software is permitted to force a link into

compliance mode at the speed indicated by the TLS field by

setting this bit in both components on a link and then initiat-

ing a hot reset on the link.

This field is read-only zero in PCIe 1.1 mode.

5

HASD

RW

0x0

Hardware Autonomous Speed Disable.

When set this bit

prevents hardware from changing the link speed for any rea-

son other than to correct unreliable link operation by reduc-

ing the link speed.

This field is read-only zero in PCIe 1.1 mode.

15:6

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

15:0

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

31:0

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

15:0

Reserved

RO

0x0

Reserved field.

Summary of Contents for 89HPES24N3A

Page 10: ...IDT Table of Contents PES24N3A User Manual iv April 10 2008 Notes...

Page 12: ...IDT List of Tables PES24N3A User Manual vi April 10 2008 Notes...

Page 14: ...IDT List of Figures PES24N3A User Manual viii April 10 2008 Notes...

Page 18: ...IDT Register List PES24N3A User Manual xii April 10 2008 Notes...

Page 64: ...IDT Link Operation PES24N3A User Manual 4 8 April 10 2008 Notes...

Page 88: ...IDT Power Management PES24N3A User Manual 7 4 April 10 2008 Notes...

Page 160: ...IDT Configuration Registers PES24N3A User Manual 9 66 April 10 2008 Notes...