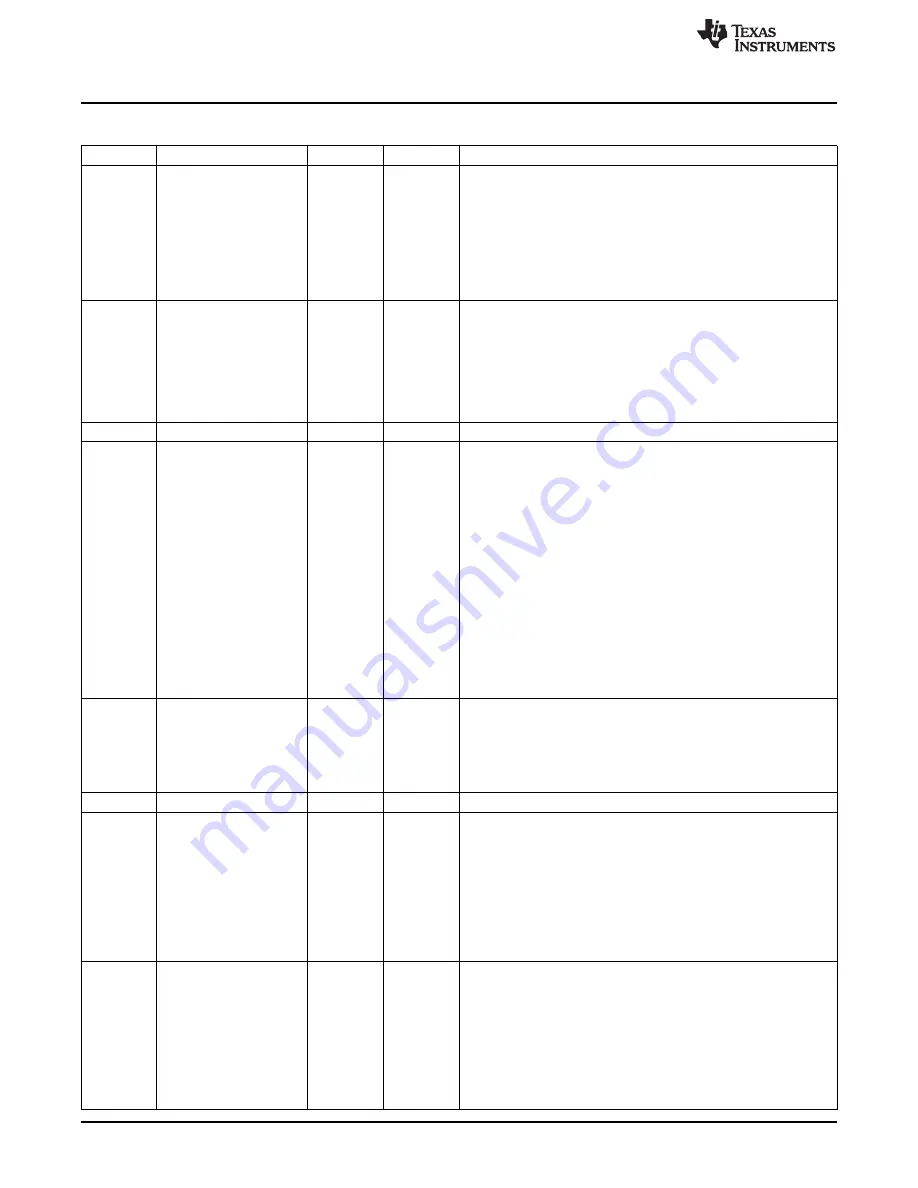

I2C Registers

Table 21-16. I2C_WE Register Field Descriptions (continued)

Bit

Field

Type

Reset

Description

9

AAS_WE

R/W

0h

Address as slave IRQ wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is in idle mode, and external master

addresses the I2C module as a slave.

This allows for the module to inform the CPU that it can check which

of the own addresses was used by the external master to access the

I2C core.

0x0 = Addressed as slave wakeup disabled

0x1 = Addressed as slave wakeup enabled

8

BF_WE

R/W

0h

Bus free IRQ wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is in idle mode and the I2C bus

became free.

This allows for the module to inform the CPU that it can initiate its

own transfer on the I2C line.

0x0 = Bus Free wakeup disabled

0x1 = Bus Free wakeup enabled

7

Reserved

R

0h

6

STC_WE

R/W

0h

Start condition IRQ wakeup set.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is in idle mode (with the functional

clock inactive) and a possible start condition is detected on the I2C

line.

The STC WakeUp is generated only if the I2C_SYSC.ClockActivity

field indicates that the functional clock can be disabled.

Note that if the functional clock is not active, the start condition is

asynchronously detected (no filtering and synchronization is used).

For this reason, it is possible that the signalized start condition to be

a glitch.

If the functional clock cannot be disabled (I2C_SYSC.ClockActivity =

10 or 11), the programmer should not enable this wakeup, since the

module has other synchronously detected WakeUp event that might

be used to exit from idle mode, only if the detected transfer is

accessing the I2C module.

0x0 = Start condition wakeup disabled

0x1 = Start condition wakeup enabled

5

GC_WE

R/W

0h

General call IRQ wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is in idle mode and a general call is

received on I2C line.

0x0 = General call wakeup disabled

0x1 = General call wakeup enabled

4

Reserved

R

0h

3

DRDY_WE

R/W

0h

Receive/Transmit data ready IRQ wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is involved into a long transfer and no

more registers accesses are performed on the interface (for example

module are set in F/S I2C master transmitter mode and FIFO is full).

If in the middle of such a transaction, the FIFO buffer needs more

data to be transferred, CPU must be informed to write (in case of

transmitter mode) or read (if receiver mode) in/from the FIFO.

0x0 = Transmit/receive data ready wakeup disabled

0x1 = Transmit/receive data ready wakeup enabled

2

ARDY_WE

R/W

0h

Register access ready IRQ wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is involved into a long transfer and no

more registers accesses are performed on the interface (for example

the module is set in F/S I2C master transmitter mode and FIFO is

full).

If the current transaction is finished, the module needs to inform

CPU about transmission completion.

0x0 = Register access ready wakeup disabled

0x1 = Register access ready wakeup enabled

3734

I2C

SPRUH73H – October 2011 – Revised April 2013

Copyright © 2011–2013, Texas Instruments Incorporated