DocID024597 Rev 5

RM0351

Universal synchronous asynchronous receiver transmitter (USART)

1411

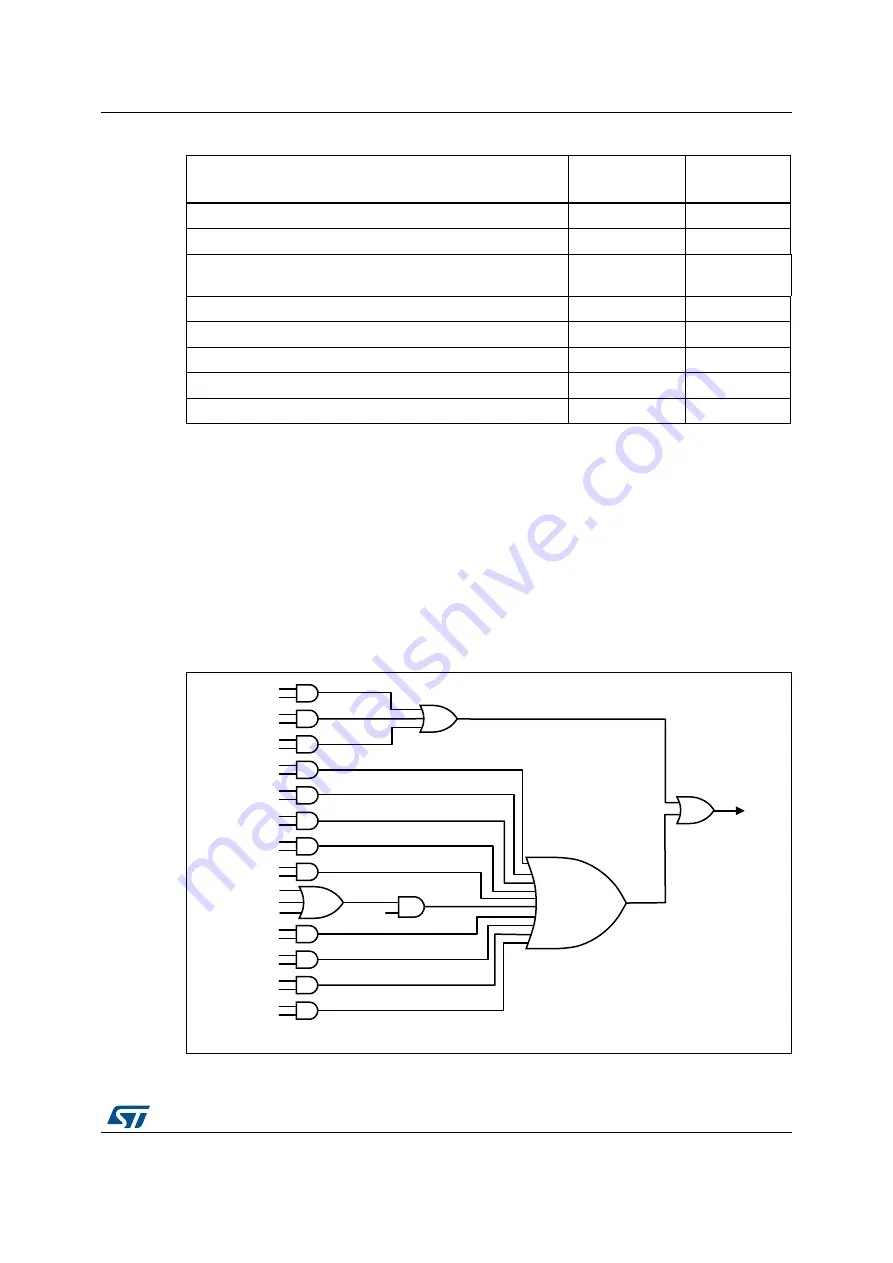

The USART interrupt events are connected to the same interrupt vector (see

•

During transmission: Transmission Complete, Transmission complete before guard

time, Clear to Send, Transmit data Register empty or Framing error (in Smartcard

mode) interrupt.

•

During reception: Idle Line detection, Overrun error, Receive data register not empty,

Parity error, LIN break detection, Noise Flag, Framing Error, Character match, etc.

These events generate an interrupt if the corresponding Enable Control Bit is set.

Figure 430. USART interrupt mapping diagram

Parity error

PE

PEIE

LIN break

LBDF

LBDIE

Noise Flag, Overrun error and Framing Error in multibuffer

communication.

NF or ORE or FE

EIE

Character match

CMF

CMIE

Receiver timeout

RTOF

RTOIE

End of Block

EOBF

EOBIE

Wakeup from Stop mode

WUF

(1)

WUFIE

Transmission complete before guard time

(2)

TCBGT

TCBGTIE

1. The WUF interrupt is active only in Stop mode.

2. Available on STM32L496xx/4A6xx devices only.

Table 239. USART interrupt requests (continued)

Interrupt event

Event flag

Enable Control

bit

06Y9

7&

7&,(

7;(

7;(,(

&76,)

&76,(

,'/(

,'/(,(

5;1(,(

25(

5;1(,(

5;1(

3(

3(,(

/%')

/%',(

&0)

&0,(

(2%)

(2%,(

:8)

:8),(

)(

1)

25(

572)

572,(

(,(

86$57

LQWHUUXSW