69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69r

lq62d-f714peg4 * Memec (Headquar

ters) - Unique

T

ech, Insight, Impact * UNDER ND

A# 12101050

MAR

VELL CONFIDENTIAL - UNA

UTHORIZED DISTRIB

UTION OR USE STRICTL

Y PR

OHIBITED

PXA300 Processor and PXA310 Processor

Vol. I: System and Timer Configuration Developers Manual

Doc. No. MV-TBD-00 Rev. A

CONFIDENTIAL

Copyright © 12/13/06 Marvell

Page 222

Document Classification: Proprietary Information

December 13, 2006

Not approved by Document Control. For review only.

8.9

Register Descriptions

8.9.1

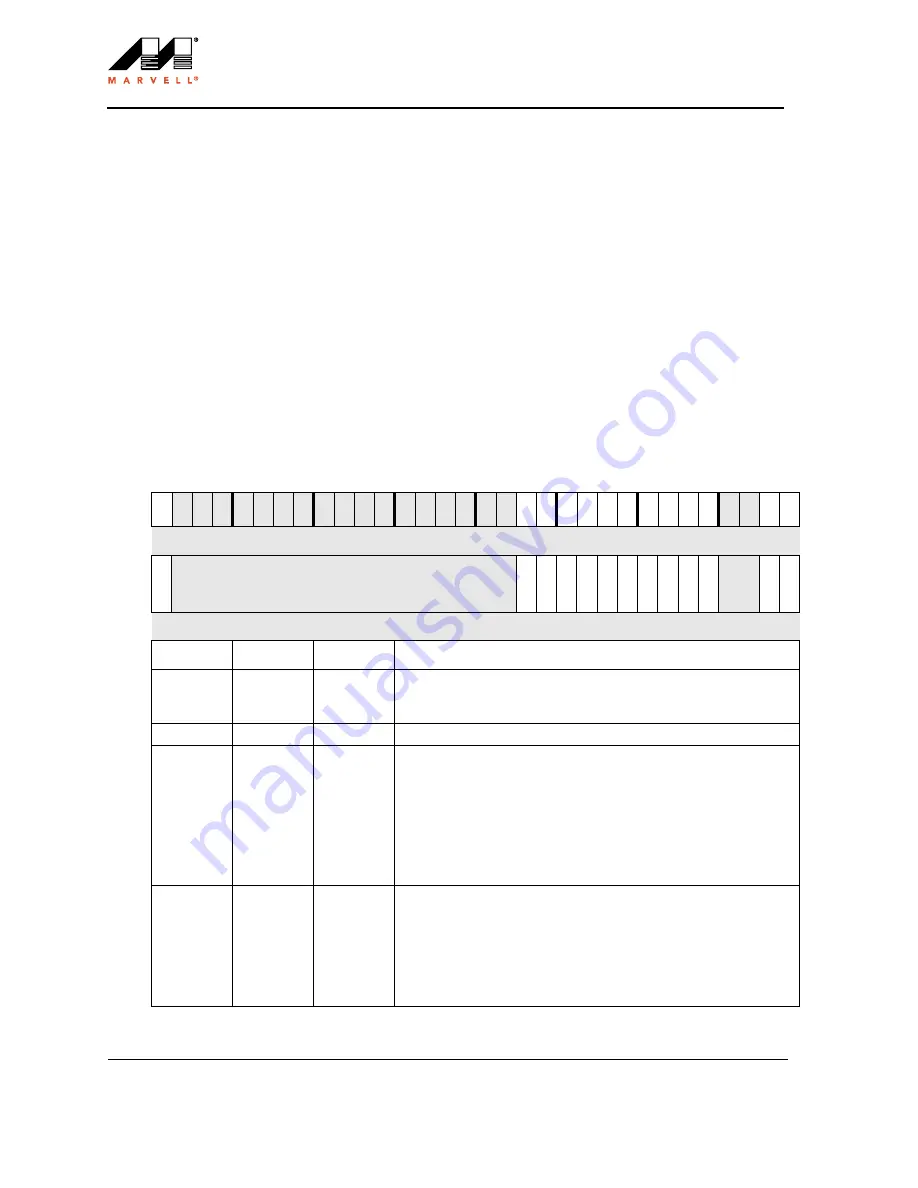

Power Management Unit Control Register (PMCR)

, controls the MPMU interrupt generation and behavior when MPMU-based

interrupt conditions occur.

A write to the PMCR requires two 32-kHz clock cycles to complete. Wait for two 32-kHz clock cycles between

writes to the PMCR or data corruption may occur.

Power-on, hardware, and watchdog resets return the PMCR bits to their reset values, as shown in

.

GPIO reset does not affect the PMCR bits.

This is a read/write register. Ignore reads from reserved bits. Write 0b0 to reserved bits.

.

Table 8-6. PMCR Bit Definitions (Sheet 1 of 2)

Physical Address

0x40F5_0000

PMCR

Services Unit

Power Management Unit

User

Settings

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

SWGR

reserved

VI

S

VI

E

TIS

TIE

reserved

reserved

reserved

reserved

reserved

reserved

reserved

BI

S

BI

E

Reset

0

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

0

0

0

0

?

?

?

?

?

?

?

? 0

†

0

†

Bits

Access

Name

Description

31

R/Write 1 to

Set

SWGR

Software GPIO Reset

1 – Assert GPIO reset to subsystems.

0 – GPIO reset not asserted to subsystems.

30:14

—

—

reserved

13

R/Write 1 to

Clear

VIS

Interrupt Status for VCC_APPS and VCC_SRAM Voltage Change Due to a

High-Temperature Condition

0 – No VCC_APPS and VCC_SRAM voltage change due to a

high-temperature condition occurred since the last time VIS was

cleared by software or reset.

1 – The interrupt was due to a VCC_APPS and VCC_SRAM voltage

change due to a high-temperature condition with VIE set.

Note : This bit will only get set if the PI2C commands for voltage change are

enabled by setting PVCR[FVE]=1

12

R/W

VIE

Interrupt Enable for VCC_APPS and VCC_SRAM Voltage Change Due to a

High-Temperature Condition

0 – Do not send interrupt to application core when the VCC_APPS and

VCC_SRAM voltages are changed due to a high-temperature

condition.

1 – Send an interrupt to the application core when the VCC_APPS and

VCC_SRAM voltages are changed due to a high-temperature

condition.