The HPS includes two general-purpose SPI master controllers and two general-purpose SPI slave controllers.

The SPI controller can connect to any other SPI device using any of the following protocols:

• Motorola SPI Protocol †

• Texas Instruments Serial Protocol (SSP) †

• National Semiconductor Microwire Protocol †

SPI Controller Overview

In order for the SPI controller to connect to a serial-master or serial-slave peripheral device, the peripheral

must have a least one of the following interfaces: †

• Motorola SPI protocol – A four-wire, full-duplex serial protocol from Motorola. The slave select line is

held high when the SPI controller is idle or disabled. For more information, refer to “Motorola SPI

Protocol”. †

• Texas Instruments Serial Protocol (SSP) – A four-wire, full-duplex serial protocol. The slave select line

used for SPI and Microwire protocols doubles as the frame indicator for the SSP protocol. For more

information, refer to “Texas Instruments Synchronous Serial Protocol (SSP)”. †

• National Semiconductor Microwire – A half-duplex serial protocol, which uses a control word transmitted

from the serial master to the target serial slave. For more information, refer to “National Semiconductor

Microwire Protocol”. You can program the FRF (frame format) bit field in the Control Register 0

(

CTRLR0

) to select which protocol is used. †

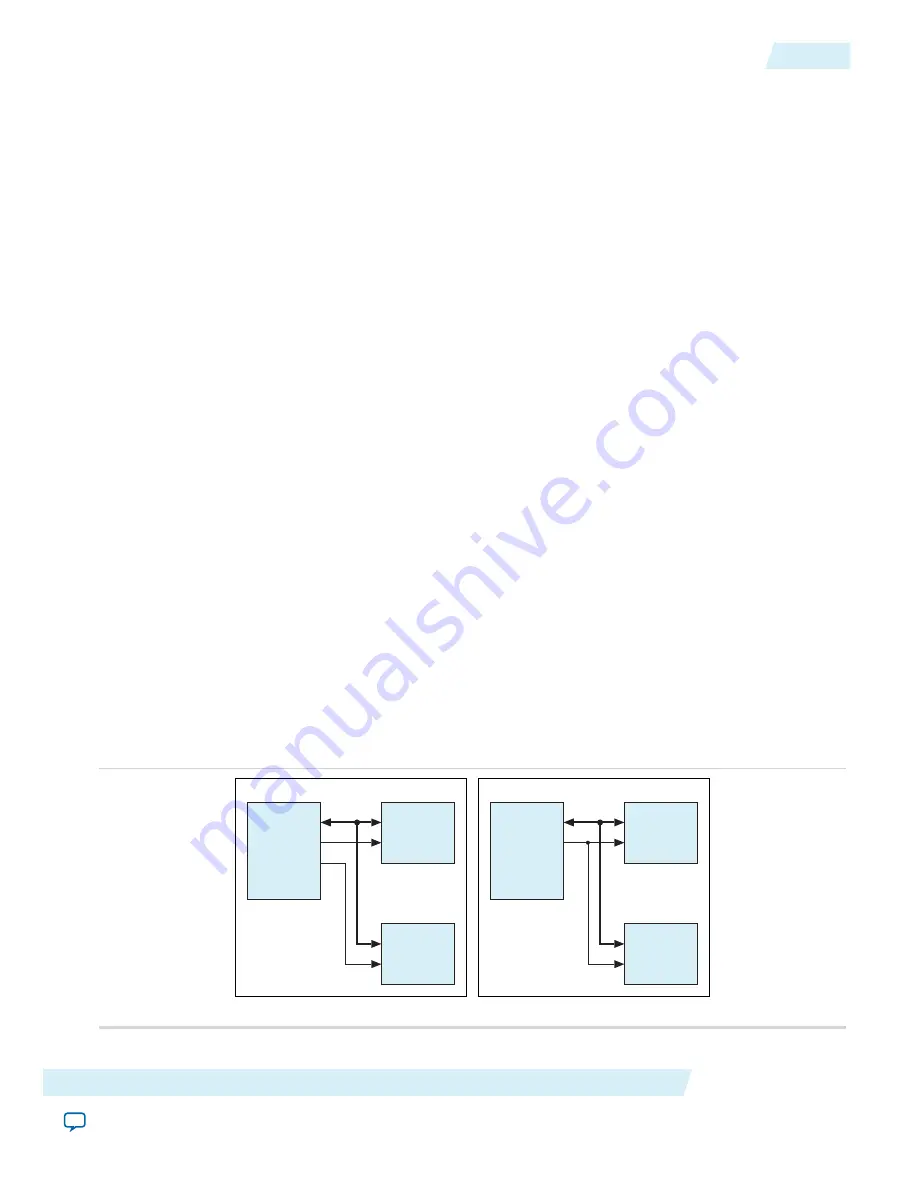

The serial protocols supported by the SPI controller allow for serial slaves to be selected or addressed using

hardware. Serial slaves are selected under the control of dedicated hardware select lines. The number of

select lines generated from the serial master is equal to the number of serial slaves present on the bus. The

serial-master device asserts the select line of the target serial slave before data transfer begins. This

architecture is illustrated in part A in the following figure. †

When implemented in software, the input select line for all serial slave devices should originate from a single

slave select output on the serial master. In this mode it is assumed that the serial master has only a single

slave select output. If there are multiple serial masters in the system, the slave select output from all masters

can be logically ANDed to generate a single slave select input for all serial slave devices. †

The main program in the software domain controls selection of the target slave device; this architecture is

illustrated in part B of the Hardware/Software Slave Selection diagram Software would control which slave

is to respond to the serial transfer request from the master device. †

Figure 19-2: Hardware/Software Slave Selection

Master

Slave

ss

ss_0

ss_1

Slave

ss

Data Bus

Master

Slave

ss

ss

Slave

ss

Data Bus

B

A

ss = Slave Select Line

Altera Corporation

SPI Controller

19-3

SPI Controller Overview

cv_54019

2013.12.30