AT32WB415

Series Reference Manual

2022.04.13

Page 203

Ver 2.00

14.3 Advanced-control timers (TMR1)

14.3.1 TMR1 introduction

The advanced-control timer TMR1 consists of a 16-bit counter supporting up and down counting modes,

four capture/compare registers, and four independent channels to achieve embedded dead-time, input

capture and programmable PWM output.

14.3.2 TMR1 main features

Souce of counter clock: internal clock, external clock an internal trigger input

16-bit up, down, up/down, repetition and encoder mode counter

Four independent channels for input capture, output compare, PWM generation, one-pulse mode

output and embedded dead-time

Three independent channesl for complementary output

TMR break function

Synchronization control between master and slave timers

Interrrupt/DMA is generated at overflow event, trigger event, break signal input and channel

event

Support TMR burst DMA transfer

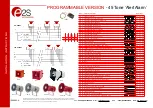

Figure 14-44 Block diagram of advanced-control timer

Input filter

C2IFP1

C1IFP1

XOR

Prescaler

Output

control

Output

control

Output

control

Output

control

C4IRAW

C3IRAW

C2IRAW

C4ORAW

C3ORAW

C2ORAW

C1ORAW

C1OUT

C1COUT

C2OUT

C3OUT

C4OUT

C2COUT

C3COUT

TRGOUT

To other timers

To ADC

BRK

Clock failure event

From clock control CSS(Clock Security System)

TMRx_BRK

TMRx_CH4

TMRx_CH3

TMRx_CH2

TMRx_CH1

TMRX_EXT

TMRx_CH1

TMRx_CH2

TMRx_CH3

TMRx_CH4

TMRx_CH1C

TMRx_CH2C

TMRx_CH3C

C1INC

Reset, enable, and up/down counting

C1IRAW

Polarity selection

Polarity selection

edge detector

prescaler

IS3

IS2

IS1

IS0

Trigger

controller

Slave mode

controller

Encoder

interface

DIV Prescaler

+/- CNT counter

Period register

Repetition

counter

Edge detector

Input filter

CxDT

(INPUT)

CxDT

(OUTPUT)

DTG

14.3.3 TMR1 functional overview

14.3.3.1 Count clock

The count clock of TMR1 can be provided by the internal clock (CK_INT), external clock (external clock

mode A and B) and internal trigger input (ISx)

Internal clock (CK_INT)

By default, the CK_INT divided by the prescaler is used to drive the counter to start counting.