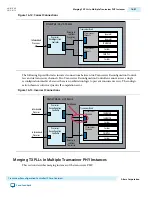

Two PHY IP Core Instances Each with Four Bonded Channels

This section describes logical channel numbering for two transceiver PHY instances, each with four

bonded channels, connected to a Transceiver Reconfiguration Controller.

When two transceiver PHY instances, each with four bonded channels, are connected to a Transceiver

Reconfiguration Controller, the reconfiguration buses of the two instances are concatenated. The

following figure and table show the order and numbering of reconfiguration interfaces. The Quartus II

software assigns the data channels logical channel numbers 0 to 3 for each transceiver PHY instance. The

Quartus II software assigns the TX PLLs logical channel numbers 4 to 7 for each transceiver PHY

instance. During Quartus II place and route, the Fitter maps the four logical TX PLLs in each transceiver

PHY instance to a single physical TX PLL.

Figure 16-11: Interface Ordering with Multiple Transceiver PHY Instances

to and from

Embedded

Controller

Transceiver

Reconfiguration

Controller

S

Interfaces 0-7

Interfaces 8-15

Reconfig to and from

Transceiver

Transceiver PHY Instance 1

Avalon-MM

Streaming Data

Streaming Data

Transceiver PHY Instance 0

Avalon-MM

Interfaces 0-3: Data Lanes

Interfaces 4-7: TX PLL

Interfaces 0-3: Data Lanes

Interfaces 4-7: TX PLL

TX and RX

Serial Data

TX and RX

Serial Data

MAC

MAC

Stratix V GX, GS, or GT Device

.

.

.

.

.

.

Table 16-29: Channel Ordering for Concatenated Transceiver Instances

Logical Interface Number

PHY Instance, Interface, or PLL

0-3

Instance 0, interfaces 0-3.

4-7

Instance 0, TX PLL. The Fitter assigns all 4 logical TX PLLs to a

single physical PLL.

8-11

Instance 1, interfaces 0-3.

UG-01080

2015.01.19

Two PHY IP Core Instances Each with Four Bonded Channels

16-53

Transceiver Reconfiguration Controller IP Core Overview

Altera Corporation

Send Feedback