Interlaken PHY IP Core...................................................................................... 7-1

Interlaken PHY Device Family Support................................................................................................... 7-2

Parameterizing the Interlaken PHY.......................................................................................................... 7-3

Interlaken PHY General Parameters.........................................................................................................7-3

Interlaken PHY Optional Port Parameters.............................................................................................. 7-5

Interlaken PHY Analog Parameters..........................................................................................................7-5

Interlaken PHY Interfaces.......................................................................................................................... 7-6

Interlaken PHY Avalon-ST TX Interface................................................................................................. 7-7

Interlaken PHY Avalon-ST RX Interface............................................................................................... 7-10

Interlaken PHY TX and RX Serial Interface.......................................................................................... 7-14

Interlaken PHY PLL Interface..................................................................................................................7-14

Interlaken Optional Clocks for Deskew..................................................................................................7-15

Interlaken PHY Register Interface and Register Descriptions............................................................ 7-16

Why Transceiver Dynamic Reconfiguration......................................................................................... 7-20

Dynamic Transceiver Reconfiguration Interface.................................................................................. 7-20

Interlaken PHY TimeQuest Timing Constraints..................................................................................7-21

Interlaken PHY Simulation Files and Example Testbench..................................................................7-21

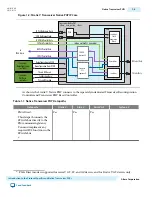

PHY IP Core for PCI Express (PIPE) .................................................................8-1

PHY for PCIe (PIPE) Device Family Support..........................................................................................8-3

PHY for PCIe (PIPE) Resource Utilization..............................................................................................8-3

Parameterizing the PHY IP Core for PCI Express (PIPE)..................................................................... 8-3

PHY for PCIe (PIPE) General Options Parameters................................................................................8-3

PHY for PCIe (PIPE) Interfaces.................................................................................................................8-6

PHY for PCIe (PIPE) Input Data from the PHY MAC..........................................................................8-7

PHY for PCIe (PIPE) Output Data to the PHY MAC..........................................................................8-11

PHY for PCIe (PIPE) Clocks....................................................................................................................8-13

PHY for PCIe (PIPE) Clock SDC Timing Constraints for Gen3 Designs.........................................8-13

PHY for PCIe (PIPE) Optional Status Interface....................................................................................8-14

PHY for PCIe (PIPE) Serial Data Interface............................................................................................8-14

PHY for PCIe (PIPE) Register Interface and Register Descriptions...................................................8-15

PHY for PCIe (PIPE) Link Equalization for Gen3 Data Rate..............................................................8-21

Phase 0.............................................................................................................................................8-22

Phase 1.............................................................................................................................................8-22

Phase 2 (Optional)......................................................................................................................... 8-22

Phase 3 (Optional)......................................................................................................................... 8-23

Recommendations for Tuning Link Partner’s Transmitter.....................................................8-23

Enabling Dynamic PMA Tuning for PCIe Gen3.................................................................................. 8-23

PHY for PCIe (PIPE) Dynamic Reconfiguration..................................................................................8-24

Logical Lane Assignment Restriction..........................................................................................8-25

PHY for PCIe (PIPE) Simulation Files and Example Testbench........................................................ 8-25

Custom PHY IP Core.......................................................................................... 9-1

Device Family Support................................................................................................................................9-2

Performance and Resource Utilization.....................................................................................................9-2

Altera Transceiver PHY IP Core User Guide

TOC-5

Altera Corporation