Table 16-32: Initial Number of Eight Bonded Channels

Instance

Channel

Logical Channel Number

Instance 0

Channel 0

0

Channel 1

1

Channel 2

2

Channel 3

3

CMU 0

4

CMU 1

5

CMU 2

6

CMU 3

7

Instance 1

Channel 0

8

Channel 1

9

CMU 0

10

CMU 1

11

Transceiver Reconfiguration Controller to PHY IP Connectivity

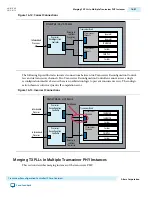

This section describes connecting a Transceiver Reconfiguration Controller to the transceiver channels

and PLLs in your design.

You can connect a single Transceiver Reconfiguration Controller to all of the transceiver channels and

PLLs in your design. You can also use multiple Transceiver Reconfiguration Controllers to facilitate

placement and routing of the FPGA. However, the three, upper or lower contiguous channels in a

transceiver bank must be connected to the same reconfiguration controller.

The following figure illustrates connections between the Transceiver Reconfiguration Controller and

transceiver channels after Quartus II compilation.

16-56

Transceiver Reconfiguration Controller to PHY IP Connectivity

UG-01080

2015.01.19

Altera Corporation

Transceiver Reconfiguration Controller IP Core Overview

Send Feedback