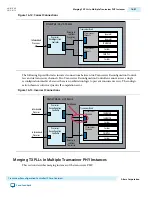

Figure 16-12: Correct Connections

Transceiver

Reconfiguration

Controller

Transceiver Bank

3 Transceiver

Channels

3 Transceiver

Channels

10 GBASE-R

(unused)

(unused)

Custom

Custom

CMU PLL

S

to Embedded

Processor

Reconfig to

and from

Transceiver

Stratix V GX, GS, or GT Device

The following figure illustrates incorrect connections between two Transceiver Reconfiguration Control‐

lers and six transceiver channels. Two Transceiver Reconfiguration Controllers cannot access a single

reconfiguration interface because there is no arbitration logic to prevent concurrent access. The configu‐

ration shown results in a Quartus II compilation error.

Figure 16-13: Incorrect Connections

3 Transceiver

Channels

Transceiver Bank

3 Transceiver

Channels

Not Allowed

Custom

10 GBASE-R

10 GBASE-R

Custom

Custom

CMU PLL

Transceiver

Reconfiguration

Controller

S

to Embedded

Processor

Transceiver

Reconfiguration

Controller

S

to Embedded

Processor

Reconfig to

and from

Transceiver

Stratix V GX, GS, or GT Device

Merging TX PLLs In Multiple Transceiver PHY Instances

This section describes merging instances of the transceiver PHY.

UG-01080

2015.01.19

Merging TX PLLs In Multiple Transceiver PHY Instances

16-57

Transceiver Reconfiguration Controller IP Core Overview

Altera Corporation

Send Feedback