Status Condition

Protocol

Mapping of Status Flags to RX Data

Value

Insertion

Basic double width

Serial RapidIO double width

RXD[62:62] = rx_

rmfifostatus[1:0]

, or

RXD[46:45] = rx_rmfifos-

tatus[1:0]

, or

RXD[30:29] = rx_

rmfifostatus[1:0]

, or

RXD[14:13] = rx_rmfifos-

tatus[1:0]

2'b10

All other protocols

Depending on the FPGA fabric to

PCS interface width either:

RXD[46:45] = rx_rmfifos-

tatus[1:0]

, or

RXD[14:13] = rx_rmfifos-

tatus[1:0]

2'b10

Deletion

Basic double width

Serial RapidIO double width

RXD[62:62] = rx_

rmfifostatus[1:0]

, or

RXD[46:45] = rx_rmfifos-

tatus[1:0]

, or

RXD[30:29] = rx_

rmfifostatus[1:0]

, or

RXD[14:13] = rx_rmfifos-

tatus[1:0]

2'b01

All other protocols

Depending on the FPGA fabric to

PCS interface width either:

RXD[46:45] = rx_rmfifos-

tatus[1:0]

, or

RXD[14:13] = rx_rmfifos-

tatus[1:0]

2'b01

Related Information

Transceiver Architecture in Arria V Devices

Word Aligner and BitSlip Parameters

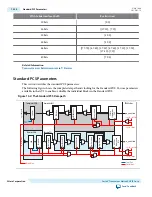

The word aligner aligns the data coming from RX PMA deserializer to a given word boundary. When the

word aligner operates in bitslip mode, the word aligner slips a single bit for every rising edge of the bit slip

control signal.

Note: For more information refer to the Word Aligner section in the

Transceiver Architecture in Arria V

Devices

.

13-18

Word Aligner and BitSlip Parameters

UG-01080

2015.01.19

Altera Corporation

Arria V Transceiver Native PHY IP Core

Send Feedback