CHAPTER 9 WATCHDOG TIMER

Preliminary User’s Manual U16846EJ1V0UD

175

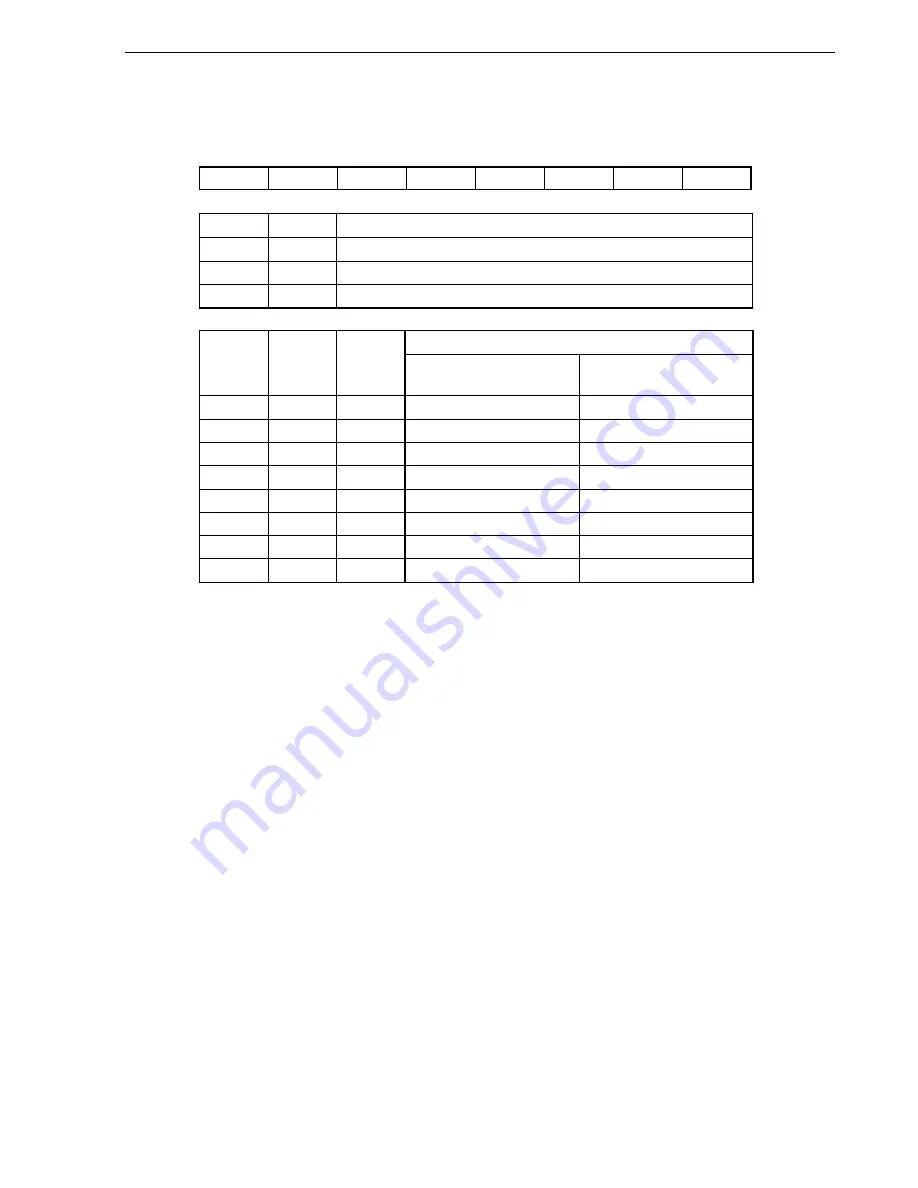

Figure 9-2. Format of Watchdog Timer Mode Register (WDTM)

0

WDCS0

1

WDCS1

2

WDCS2

3

WDCS3

4

WDCS4

5

1

6

1

7

0

Symbol

WDTM

Address: FF98H After reset: 67H R/W

WDCS4

Note 1

WDCS3

Note 1

Operation

clock

selection

0

0

Ring-OSC clock (f

R

)

0

1

High-speed system clock (f

XP

)

1

×

Watchdog timer operation stopped

Overflow time setting

WDCS2

Note 2

WDCS1

Note 2

WDCS0

Note 2

During Ring-OSC clock

operation

During high-speed system clock

operation

0 0 0

f

R

/2

11

(8.53 ms)

f

XP

/2

13

(819.2

µ

s)

0 0 1

f

R

/2

12

(17.07 ms)

f

XP

/2

14

(1.64 ms)

0 1 0

f

R

/2

13

(34.13 ms)

f

XP

/2

15

(3.28 ms)

0 1 1

f

R

/2

14

(68.27 ms)

f

XP

/2

16

(6.55 ms)

1 0 0

f

R

/2

15

(136.53 ms)

f

XP

/2

17

(13.11 ms)

1 0 1

f

R

/2

16

(273.07 ms)

f

XP

/2

18

(26.21 ms)

1 1 0

f

R

/2

17

(546.13 ms)

f

XP

/2

19

(52.43 ms)

1 1 1

f

R

/2

18

(1.09 s)

f

XP

/2

20

(104.86 ms)

Notes 1. If “Ring-OSC cannot be stopped” is specified by the option byte, this cannot be set. The Ring-

OSC clock will be selected no matter what value is written.

2. Reset is released at the maximum cycle (WDCS2, 1, 0 = 1, 1, 1).

Cautions 1. If data is written to WDTM, a wait cycle is generated. For details, see CHAPTER 25

CAUTIONS FOR WAIT.

2. Set bits 7, 6, and 5 to 0, 1, and 1, respectively (when “Ring-OSC cannot be stopped”

is selected by the option byte, other values are ignored).

3. After reset is released, WDTM can be written only once by an 8-bit memory

manipulation instruction. If writing is attempted a second time, an internal reset

signal is generated. If the source clock to the watchdog timer is stopped, however,

an internal reset signal is generated when the source clock to the watchdog timer

resumes operation.

4. WDTM cannot be set by a 1-bit memory manipulation instruction.

5. If “Ring-OSC can be stopped by software” is selected by the option byte and the

watchdog timer is stopped by setting WDCS4 to 1, the watchdog timer does not

resume operation even if WDCS4 is cleared to 0. In addition, the internal reset signal

is not generated.

Remarks 1. f

R

: Ring-OSC clock oscillation frequency

2. f

XP

: High-speed system clock oscillation frequency

3.

×

: Don’t care

4. Figures in parentheses apply to operation at f

R

= 240 kHz (TYP.), f

XP

= 10 MHz