CHAPTER 6 16-BIT TIMER/EVENT COUNTER 00

Preliminary User’s Manual U16846EJ1V0UD

107

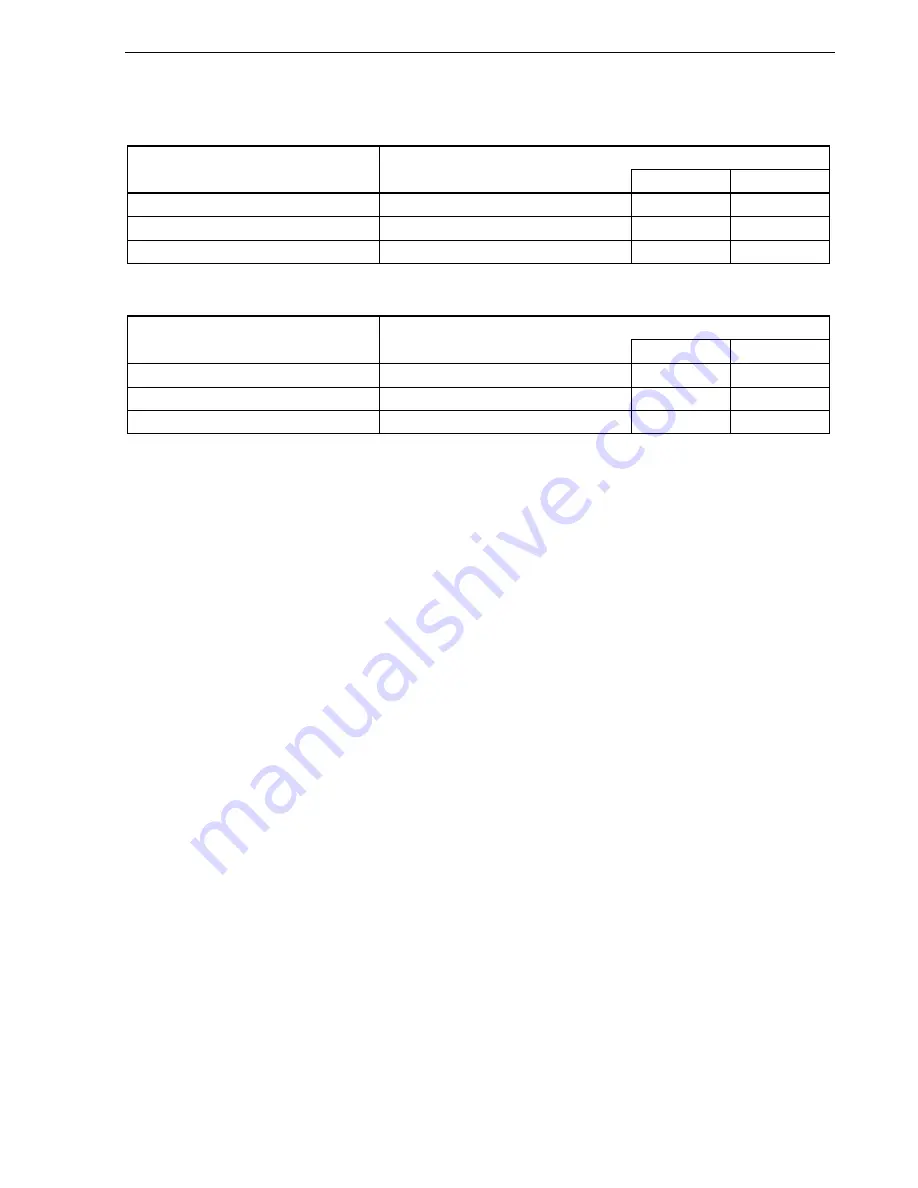

Table 6-2. CR000 Capture Trigger and Valid Edges of TI000 and TI010 Pins

(1) TI000 pin valid edge selected as capture trigger (CRC001 = 1, CRC000 = 1)

TI000 Pin Valid Edge

CR000 Capture Trigger

ES001

ES000

Falling edge

Rising edge

0

1

Rising edge

Falling edge

0

0

No capture operation

Both rising and falling edges

1

1

(2) TI010 pin valid edge selected as capture trigger (CRC001 = 0, CRC000 = 1)

TI010 Pin Valid Edge

CR000 Capture Trigger

ES101

ES100

Falling edge

Falling edge

0

0

Rising edge

Rising edge

0

1

Both rising and falling edges

Both rising and falling edges

1

1

Remarks 1. Setting ES001, ES000 = 1, 0 and ES101, ES100 = 1, 0 is prohibited.

2.

ES001, ES000:

Bits 5 and 4 of prescaler mode register 00 (PRM00)

ES101, ES100:

Bits 7 and 6 of prescaler mode register 00 (PRM00)

CRC001, CRC000: Bits 1 and 0 of capture/compare control register 00 (CRC00)

Cautions 1. Set a value other than 0000H in CR000 in the mode in which clear & start occurs on a match

of TM00 and CR000.

2. If CR000 is set to 0000H in the free-running mode and in the clear mode using the valid edge

of the TI000 pin, an interrupt request (INTTM000) is generated when the value of CR000

changes from 0000H to 0001H following TM00 overflow (FFFFH). Moreover, INTTM000 is

generated after a match of TM00 and CR000 is detected, a valid edge of the TI010 pin is

detected, and the timer is cleared by a one-shot trigger.

3. When P01 is used for the valid edge input of the TI010 pin, it cannot be used as the timer

output (TO00). Moreover, when P01 is used as TO00, it cannot be used for the valid edge

input of the TI010 pin.

4. When CR000 is used as a capture register, read data is undefined if the register read time

and capture trigger input conflict (the capture data itself is the correct value).

If count stop input and capture trigger input conflict, the captured data is undefined.

5. Do not rewrite CR000 during TM00 operation.