Rev. 5.00, 12/03, page 1001 of 1088

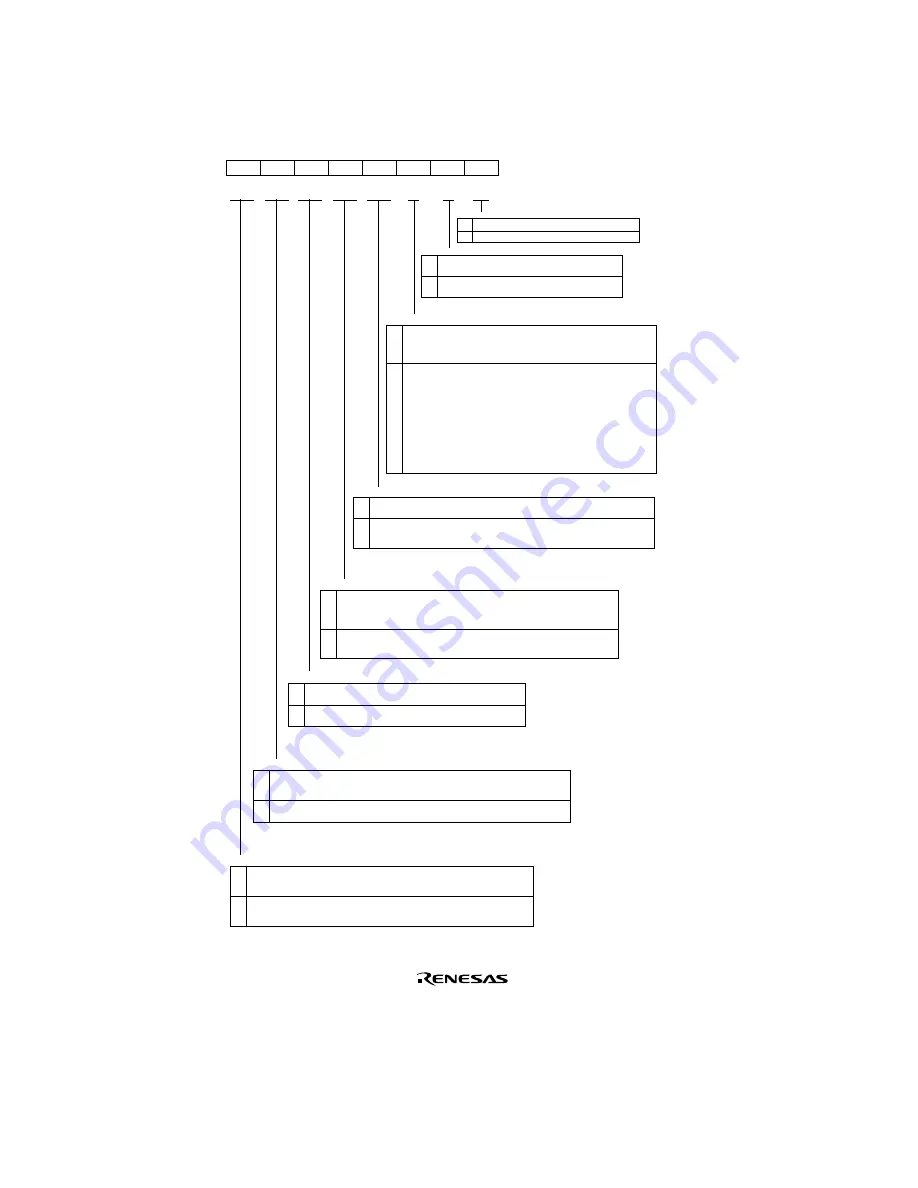

SSR0—Serial Status Register 0

H'FF7C

Smart Card Interface 0

7

TDRE

1

R/(W)

*

6

RDRF

0

R/(W)

*

5

ORER

0

R/(W)

*

4

ERS

0

R/(W)

*

3

PER

0

R/(W)

*

0

MPBT

0

R/W

2

TEND

1

R

1

MPB

0

R

0

Transmit Data Register Empty

0

Receive Data Register Full

*

0

Overrun Error

0

Error Signal Status

*

0

Parity Error

0

Transmit End

Transmission in progress

[Clearing conditions]

· When 0 is written to TDRE after reading TDRE = 1

· When the DTC is activated by a TXI interrupt and writes data to TDR

0

Multiprocessor Bit

[Clearing condition]

When data with a 0 multiprocessor bit is received

*

[Setting condition]

When data with a 1 multiprocessor bit is received

Multiprocessor Bit Transfer

0

1

Data with a 0 multiprocessor bit is transmitted

Data with a 1 multiprocessor bit is transmitted

Bit

Initial value

Read/Write

:

:

:

Transmission has ended

[Setting conditions]

· On reset, or in standby mode or module stop mode

· When the TE bit in SCR is 0 and the ERS bit is 0

· When TDRE = 1 and ERS = 0 (normal transmission) 2.5 etu after

transmission of a 1-byte serial character when GM = 0 and BLK = 0

· When TDRE = 1 and ERS = 0 (normal transmission) 1.5 etu after

transmission of a 1-byte serial character when GM = 0 and BLK = 1

· When TDRE = 1 and ERS = 0 (normal transmission) 1.0 etu after

transmission of a 1-byte serial character when GM = 1 and BLK = 0

· When TDRE = 1 and ERS = 0 (normal transmission) 1.0 etu after

transmission of a 1-byte serial character when GM = 1 and BLK = 1

[Clearing condition]

When 0 is written to PER after reading PER = 1

*

1

[Setting condition]

When, in reception, the number of 1 bits in the receive data plus the parity bit

does not match the parity setting (even or odd) specified by the O/

E

bit in SMR

*

2

Data has been received normally, and there is no error signal

[Clearing conditions]

· On reset, or in standby mode or module stop mode

· When 0 is written to ERS after reading ERS = 1

Error signal indicating detection of parity error has been sent by receiving device

[Setting condition]

When the error signal is sampled at the low level

[Clearing condition]

When 0 is written to ORER after reading ORER = 1

*

1

[Setting condition]

When the next serial reception is completed while RDRF = 1

*

2

[Clearing conditions]

· When 0 is written to RDRF after reading RDRF = 1

· When the DTC is activated by an RXI interrupt and reads data from RDR

[Setting condition]

When serial reception ends normally and receive data is transferred from RSR to RDR

[Clearing conditions]

· When 0 is written to TDRE after reading TDRE = 1

· When the DTC is activated by a TXI interrupt and writes data to TDR

[Setting conditions]

· When the TE bit in SCR is 0

· When data is transferred from TDR to TSR and data can be written to TDR

1

1

1

1

1

1

1

Note:

*

Retains its previous state when the RE bit in SCR is

cleared to 0 with a multiprocessor format.

Note:

*

Clearing the TE bit in SCR to 0 does not affect the ERS flag, which retains its prior state.

Note:

*

RDR and the RDRF flag are not affected and retain their previous values when an error is detected during reception or when the RE bit

in SCR is cleared to 0.

If reception of the next data is completed while the RDRF flag is still set to 1, an overrun error will occur and the receive data will be lost.

Notes: 1. The PER flag is not affected and retains its previous state when the RE bit in SCR is cleared to 0.

2. If a parity error occurs, the receive data is transferred to RDR but the RDRF flag is not set. Serial reception

cannot be continued while the PER flag is set to 1. In synchronous mode, serial transmission is also disabled.

Notes: 1. The ORER flag is not affected and retains its previous state when the RE bit in SCR is cleared to 0.

2. The receive data prior to the overrun error is retained in RDR, and data received subsequently is lost. Serial reception

cannot be continued while the ORER flag is set to 1. In synchronous mode, serial transmission is also disabled.

Note: etu (Elementary Time Unit): Time for transfer of 1 bit

Notes:

*

Can only be written with 0 for flag clearing.

Содержание H8S/2318 series

Страница 2: ......

Страница 6: ...Rev 5 00 12 03 page vi of xxx...

Страница 12: ...Rev 5 00 12 03 page xii of xxx...

Страница 30: ...Rev 5 00 12 03 page xxx of xxx...

Страница 54: ...Rev 5 00 12 03 page 24 of 1088...

Страница 98: ...Rev 5 00 12 03 page 68 of 1088...

Страница 128: ...Rev 5 00 12 03 page 98 of 1088...

Страница 138: ...Rev 5 00 12 03 page 108 of 1088...

Страница 168: ...Rev 5 00 12 03 page 138 of 1088...

Страница 212: ...Rev 5 00 12 03 page 182 of 1088...

Страница 324: ...Rev 5 00 12 03 page 294 of 1088...

Страница 436: ...Rev 5 00 12 03 page 406 of 1088...

Страница 546: ...Rev 5 00 12 03 page 516 of 1088...

Страница 580: ...Rev 5 00 12 03 page 550 of 1088...

Страница 822: ...Rev 5 00 12 03 page 792 of 1088...

Страница 876: ...Rev 5 00 12 03 page 846 of 1088...

Страница 901: ...Rev 5 00 12 03 page 871 of 1088 A 2 Instruction Codes Table A 2 shows the instruction codes...

Страница 1121: ...H8S 2319 Group H8S 2318 Group Hardware Manual REJ09B0089 0500O...