MOTOROLA

Chapter 27. SCC BISYNC Mode

27-11

Part V. The Communications Processor Module

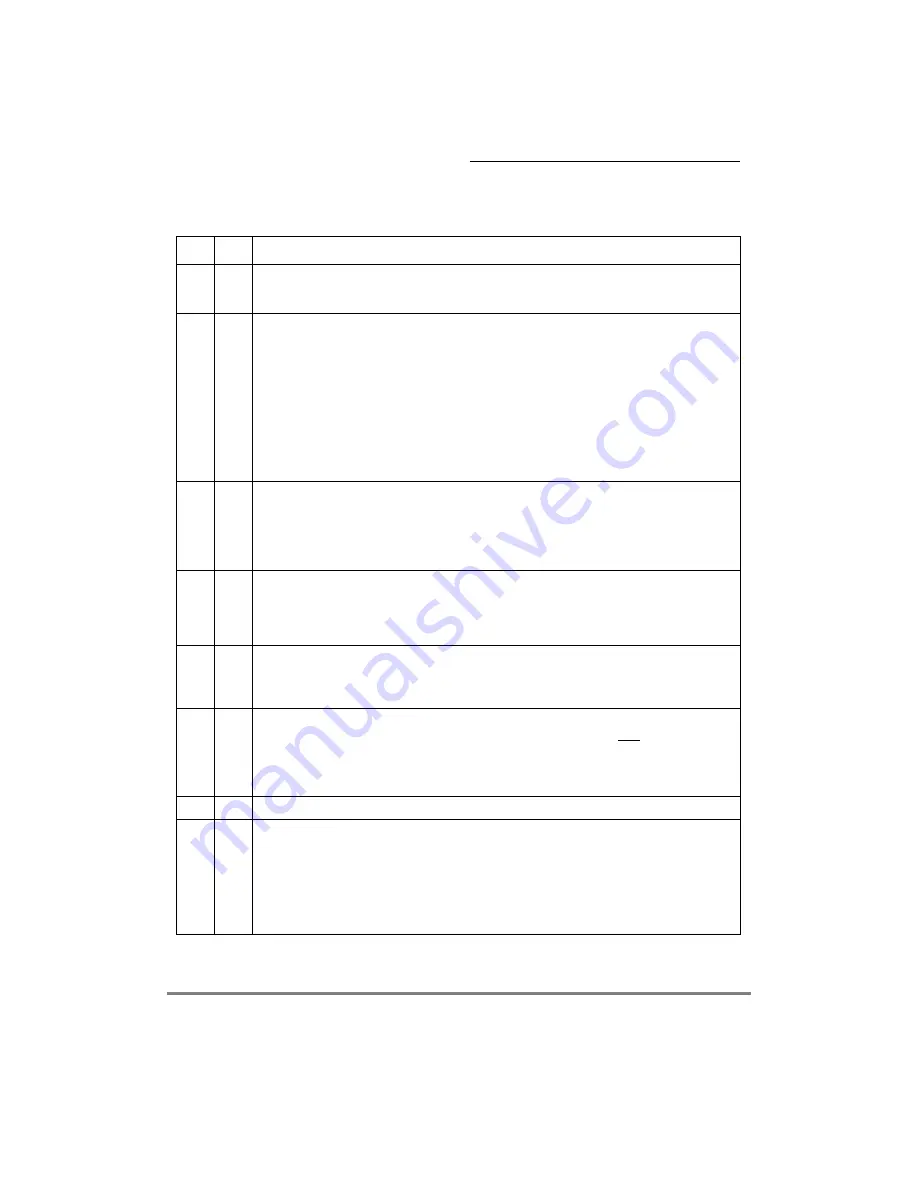

Table 27-10 describes PSMR Þelds.

Table 27-10. PSMR Field Descriptions

Bits

Name

Description

0Ð3

NOS

Minimum number of SYN1ÐSYN2 pairs (deÞned in DSR) sent between or before messages.If NOS =

0000, one pair is sent. If NOS = 1111, 16 pairs are sent. The entire pair is always sent, regardless of

how GSMR[SYNL) is set. NOS can be modiÞed on-the-ßy.

4Ð5

CRC

CRC selection.

x0 Reserved.

01 CRC16 (BISYNC). X16 + X15 + X2 + 1. PRCRC and PTCRC should be initialized to all zeros or all

ones before the channel is enabled. In either case, the transmitter sends the calculated CRC

noninverted and the receiver checks the CRC against zero. Eight-bit data characters (without

parity) are conÞgured when CRC16 is chosen.

11 LRC (sum check). (BISYNC). For even LRC, initialize PRCRC and PTCRC to zeroes before the

channel is enabled; for odd LRC, they should be initialized to ones.

Note that the receiver checks character parity when BCS is programmed to LRC and the receiver

is not in transparent mode. The transmitter sends character parity when BCS is programmed to

LRC and the transmitter is not in transparent mode. Use of parity in BISYNC assumes that 7-bit

data characters are being used.

6

RBCS Receive BCS. The receiver internally stores two BCS calculations separated by an eight serial clock

delay to allow examination of a received byte to determine whether it should used in BCS calculation.

0 Disable receive BCS.

1 Enable receive BCS. Should be set (or reset) within the time taken to receive the following data

byte. When RBCS is reset, BCS calculations exclude the latest fully received data byte. When

RBCS is set, BCS calculations continue as normal.

7

RTR

Receiver transparent mode.

0 Normal receiver mode with SYNC stripping and control character recognition.

1 Transparent receiver mode. SYNCs, DLEs, and control characters are recognized only after a

leading DLE character. The receiver calculates the CRC16 sequence even if it is programmed to

LRC while in transparent mode. Initialize PRCRC to the CRC16 preset value before setting RTR.

8

RVD

Reverse data.

0 Normal operation.

1 Any portion of this SCC deÞned to operate in BISYNC mode operates by reversing the character bit

order and sending the msb Þrst.

9

DRT

Disable receiver while sending. DRT should not be set for typical BISYNC operation.

0 Normal operation.

1 As the SCC sends data, the receiver is disabled and gated by the internal RTS signal. This helps if

the BISYNC channel is being conÞgured onto a multidrop line and the user does not want to receive

its own transmission. Although BISYNC usually uses a half-duplex protocol, the receiver is not

actually disabled during transmission.

10Ð11 Ñ

Reserved, should be cleared.

12Ð13 RPM

Receiver parity mode. Selects the type of parity check that the receiver performs. RPM can be

modiÞed on-the-ßy and is ignored unless CRC = 11 (LRC). Receive parity errors cannot be disabled

but can be ignored.

00 Odd parity. The transmitter counts ones in the data word. If the sum is not odd, the parity bit is set

to ensure an odd number. An even sum indicates a transmission error.

01 Low parity. If the parity bit is not low, a parity error is reported.

10 Even parity. An even number must result from the calculation performed at both ends of the line.

11 High parity. If the parity bit is not high, a parity error is reported.

Содержание MPC860 PowerQUICC

Страница 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Страница 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Страница 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Страница 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Страница 1106: ......