23-14

MPC860 PowerQUICC UserÕs Manual

MOTOROLA

Part V. The Communications Processor Module

6

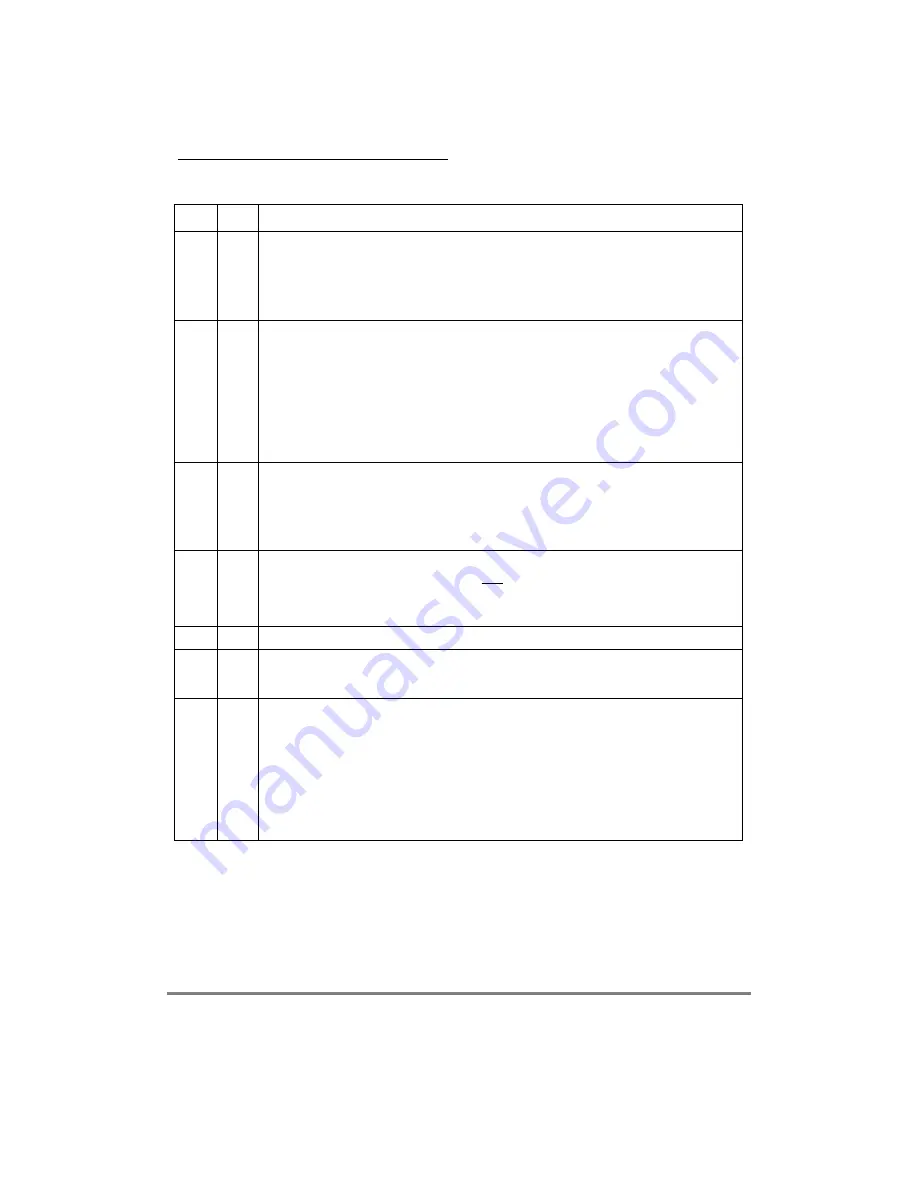

FRZ

Freeze transmission. Allows the UART transmitter to pause and later continue from that point.

0 Normal operation. If the buffer was previously frozen, it resumes transmission from the next

character in the same buffer that was frozen.

1 The SCC completes transmission of any data already transferred to the Tx FIFO (the number of

characters depends on GSMR_H[TFL]) and then freezes. After FRZ is cleared, transmission

resumes from the next character.

7

RZS

Receive zero stop bits.

0 The receiver operates normally, but at least one stop bit is needed between characters. A framing

error is issued if a stop bit is missing. Break status is set if an all-zero character is received with a

zero stop bit.

1 ConÞgures the receiver to receive data without stop bits. Useful in V.14 applications where SCC

UART controller data is supplied synchronously and all stop bits of a particular character can be

omitted for cross-network rate adaptation. RZS should be set only if SYN is set. The receiver

continues if a stop bit is missing. If the stop bit is a zero, the next bit is considered the Þrst data bit

of the next character. A framing error is issued if a stop bit is missing, but a break status is reported

only after two consecutive break characters have no stop bits.

8

SYN

Synchronous mode.

0 Normal asynchronous operation. GSMR_L[TENC,RENC] must select NRZ and GSMR_L[TDCR,

RDCR] select either 8

´

, 16

´

, or 32

´

. 16

´

is recommended for most applications.

1 Synchronous SCC UART controller using 1

´

clock (isochronous UART operation).

GSMR_L[TENC, RENC] must select NRZ and GSMR_L[RDCR, TDCR] select 1

´

mode. A bit is

transferred with each clock and is synchronous to the clock, which can be internal or external.

9

DRT

Disable receiver while transmitting.

0 Normal operation.

1 While the SCC is sending data, the internal RTS disables and gates the receiver. Useful for a

multidrop conÞguration in which the user does not want to receive its own transmission. For

multidrop UART mode, set the BDsÕ preamble bit, TxBD[P].

10

Ñ

Reserved, should be cleared.

11

PEN

Parity enable.

0 No parity.

1 Parity is enabled and determined by the parity mode bits.

12Ð13,

14Ð15

RPM,

TPM

Receiver/transmitter parity mode. Selects the type of parity check the receiver/transmitter performs;

can be modiÞed on-the-ßy. Receive parity errors can be ignored but not disabled.

00 Odd parity. If a transmitter counts an even number of ones in the data word, it sets the parity bit so

an odd number is sent. If a receiver receives an even number, a parity error is reported.

01 Low parity (space parity). A transmitter sends a zero in the parity bit position. If a receiver does

not read a 0 in the parity bit, a parity error is reported.

10 Even parity. Like odd parity, the transmitter adjusts the parity bit, as necessary, to ensure that the

receiver receives an even number of one bits; otherwise, a parity error is reported.

11 High parity (mark parity). The transmitter sends a one in the parity bit position. If the receiver does

not read a 1 in the parity bit, a parity error is reported.

Table 23-9. PSMR UART Field Descriptions (Continued)

Bit

Name

Description

Содержание MPC860 PowerQUICC

Страница 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Страница 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Страница 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Страница 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Страница 1106: ......