MOTOROLA

Chapter 23. SCC UART Mode

23-13

Part V. The Communications Processor Module

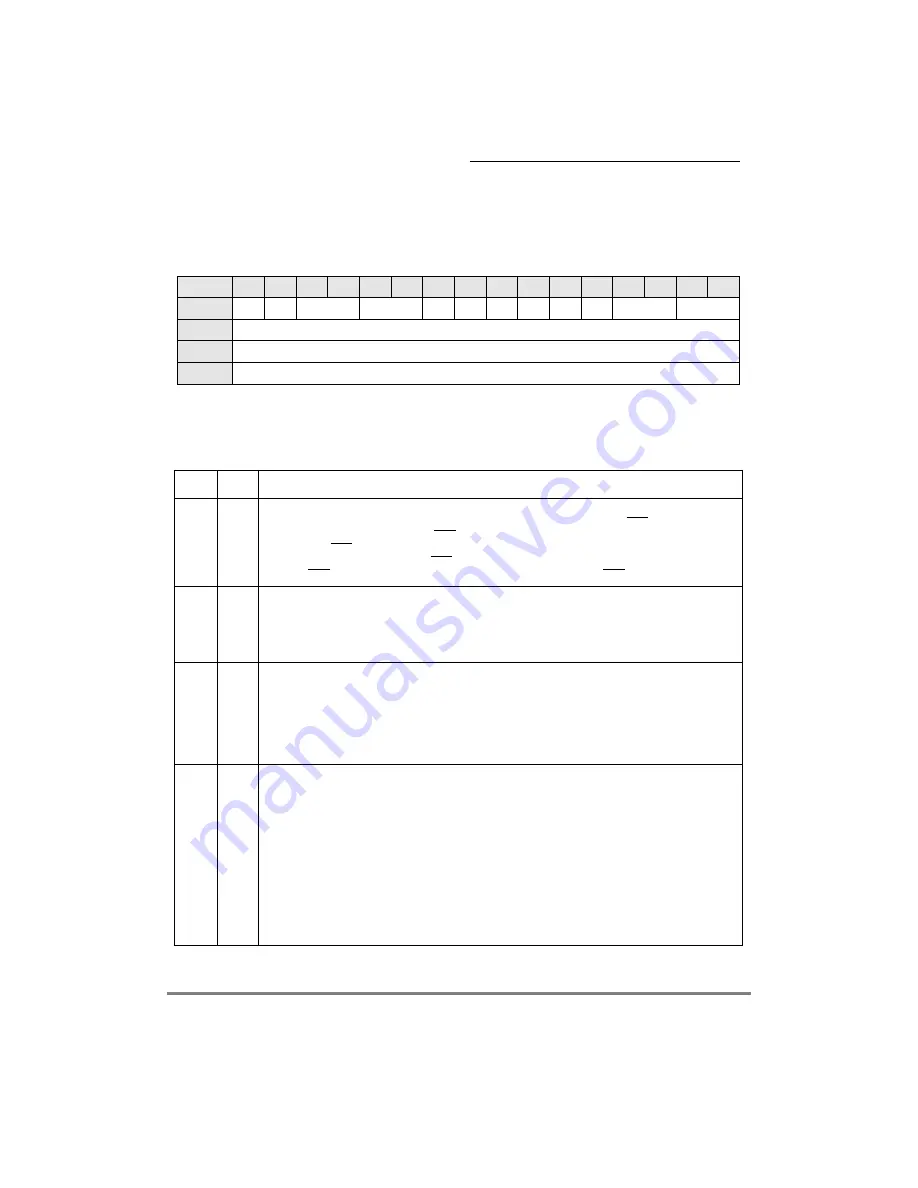

23.16 UART Mode Register (PSMR)

For UART mode, the SCC protocol-speciÞc mode register (PSMR) is called the UART

mode register. Many bits can be modiÞed while the receiver and transmitter are enabled.

Figure 23-6 shows the PSMR in UART mode.

Table 23-9 describes PSMR UART Þelds.

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

FLC

SL

CL

UM

FRZ

RZS SYN DRT

Ñ

PEN

RPM

TPM

Reset

0

R/W

R/W

Addr

0xA08 (PSMR1), 0xA28 (PSMR2), 0xA48 (PSMR3), 0xA68 (PSMR4)

Figure 23-6. Protocol-Specific Mode Register for UART (PSMR)

Table 23-9. PSMR UART Field Descriptions

Bit

Name

Description

0

FLC

Flow control.

0 Normal operation. The GSMR and port C registers determine the mode of CTS.

1 Asynchronous ßow control. When CTS is negated, the transmitter stops at the end of the current

character. If CTS is negated past the middle of the current character, the next full character is sent

before transmission stops. When CTS is asserted again, transmission continues where it left off

and no CTS lost error is reported. Only idle characters are sent while CTS is negated.

1

SL

Stop length. Selects the number of stop bits the SCC sends. SL can be modiÞed on-the-ßy. The

receiver is always enabled for one stop bit unless the SCC UART is in synchronous mode and

PSMR[RZS] is set. Fractional stop bits are conÞgured in the DSR.

0 One stop bit.

1 Two stop bits.

2Ð3

CL

Character length. Determines the number of data bits in the character, not including optional parity or

multidrop address bits. If a character is less than 8 bits, most-signiÞcant bits are received as zeros

and are ignored when the character is sent. CL can be modiÞed on-the-ßy.

00

5 data bits

01

6 data bits

10

7 data bits

11

8 data bits

4Ð5

UM

UART mode. Selects the asynchronous channel protocol. UM can be modiÞed on-the-ßy.

00 Normal UART operation. Multidrop mode is disabled and idle-line wake-up mode is selected. The

UART receiver leaves hunt mode by receiving an idle character (all ones).

01 Manual multidrop mode. An additional address/data bit is sent with each character. Multidrop

asynchronous modes are compatible with the MC68681 DUART, MC68HC11 SCI, DSP56000

SCI, and Intel 8051 serial interface. The receiver leaves hunt mode when the address/data bit is a

one, indicating the received character is an address that all inactive processors must process.

The controller receives the address character and writes it to a new buffer. The core then

compares the written address with its own address and decides whether to ignore or process

subsequent characters.

10 Reserved.

11 Automatic multidrop mode. The CPM compares the address of an incoming address character

with UADDR

x

parameter RAM values; subsequent data is accepted only if a match occurs.

Содержание MPC860 PowerQUICC

Страница 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Страница 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Страница 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Страница 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Страница 1106: ......