MOTOROLA

Chapter 37. System Development and Debugging

37-7

Part VI. Debug and Test

address is the Þrst address in the program trace cycle buffer. When using window trace,

latching of VF, VFLS, and the address of the cycles marked as program trace cycle should

all start immediately after the Þrst VSYNC is recognized on the VF pins. The start address

of the trace window should be calculated according to the Þrst two VF pin reports. Assume

VF1 and VF2 are the Þrst two VF pin reports and T1 and T2 are the two addresses of the

Þrst two cycles marked with the program trace cycle attribute that were latched in the trace

buffer. Use Table 37-5 to calculate the trace window start address.

37.1.5.4 Detecting the Assertion/Negation of VSYNC

Since the VF pins are used for reporting both instruction type and queue ßush information,

the external hardware must take special care when trying to detect entry and exit of the

VSYNC state. When VF = 0b011, it is a VSYNC entry or exit report only if the prior value

of VF was 0b000, 0b001, or 0b010.

37.1.5.5 Detecting the Trace Window End Address

The information on the status pins that describes the last fetched instruction and last

queue/history buffer ßush, changes every clock. Cycles marked as program trace cycle are

generated on the external bus only when the system interface unit (SIU) arbitrates over the

external bus. Therefore, there is a delay between when a program trace cycle is reported as

performed and the time that this cycle can be detected on the external bus.

When the user exits VSYNC state (through the serial interface of the development port), the

core delays the report of VSYNC occurring on the VF pins until all addresses marked with

the program trace cycle attribute are externally visible. Therefore, the external hardware

should stop sampling VF, VFLS, and the address of the cycles marked as program trace

cycle immediately after VF = VSYNC. The last two instructions reported on the VF pins

are not always valid and should be ignored.

37.1.5.6 EfÞcient Trace Information Capture

To store all information generated on the pins during program trace (5 bits per clock + 30

bits per show cycle) a large memory buffer is required. However, because this information

includes events that were canceled, some of this information can be discarded. External

hardware can be added to eliminate all canceled instructions and report only on taken/not

taken branches, indirect ßow change, and the number of sequential instructions after the

last ßow change.

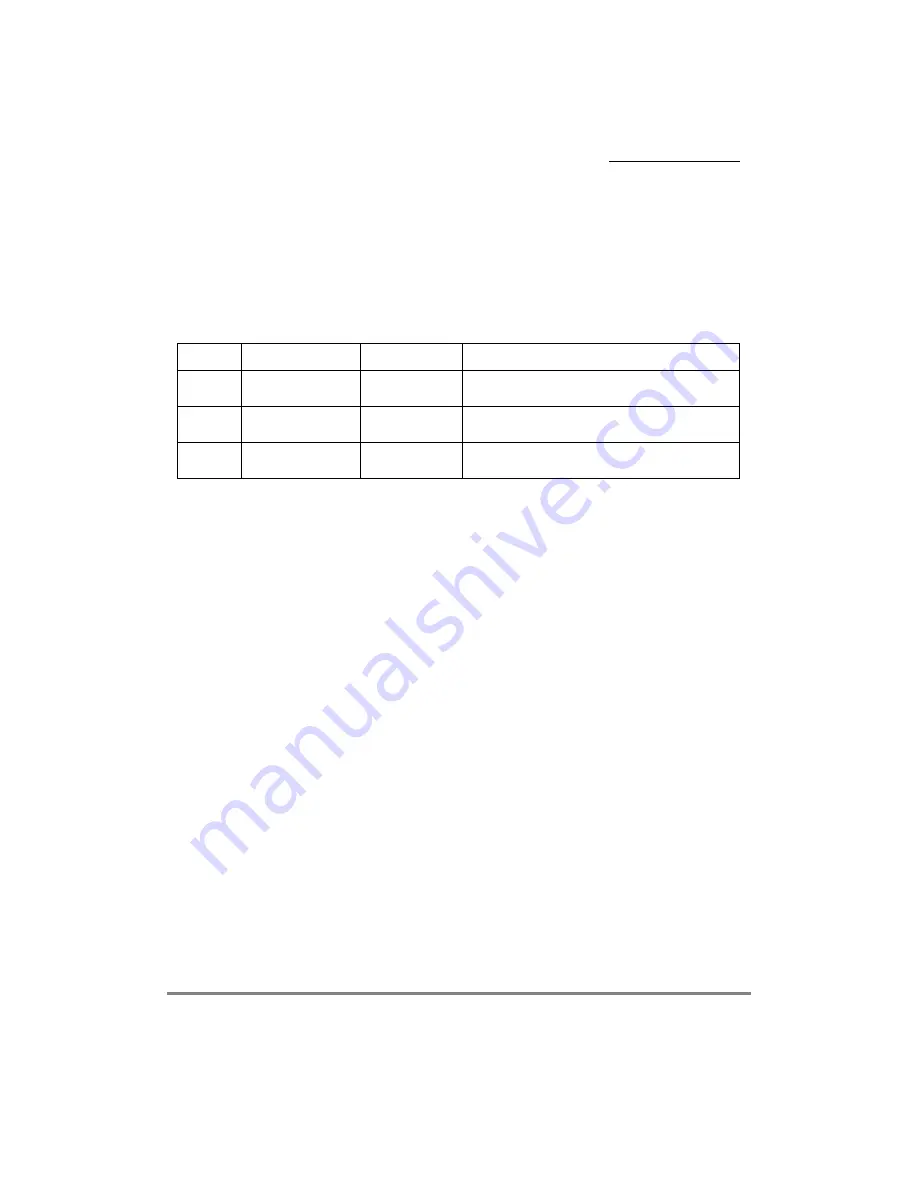

Table 37-5. Detecting the Trace Buffer Start Point

VF1

VF2

Starting Point

Description

011

VSYNC

001

Sequential

T1

VSYNC asserted. Followed by a sequential instruction.

The start address is T1.

011

VSYNC

110

Branch direct taken

T1 - 4 +

Offset(T1 - 4)

VSYNC asserted. Followed by a taken direct branch.

The start address is the target of the direct branch.

011

VSYNC

101

Branch indirect taken

T2

VSYNC asserted. Followed by a taken indirect branch.

The start address is the target of the indirect branch.

Содержание MPC860 PowerQUICC

Страница 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Страница 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Страница 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Страница 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Страница 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Страница 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Страница 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Страница 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Страница 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Страница 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Страница 1106: ......