V04.00 | 2021/05

239

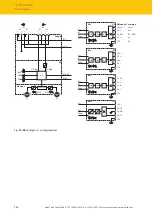

14.12 Block diagrams

ERR

BUS

PWR

µC

Supply

µC

+

2

–

3

+

1

–

4

V1

V2

+

2

–

3

+

1

–

4

V1

V2

X1

X2

IN Diag

IN Diag

V1 Diag

V2 Diag

OUT Diag

OUT Diag

P2

P1

ETH2

ETH1

Ethernet

Ethernet

1 V

AUX1

4 IN

3 V1 –

100 mA per channel

Input

8DIP-D

500 mA per group

500 mA per group

500 mA per group

8DOP

4DIP-4DOP

Input

1 V

AUX2

4 OUT

3 V2 –

Output

Output

V1 +

V1 +

IN Diag

1 V

AUX1

4 IN

3 V1 –

500 mA per group

Input

8DIP

4DIP-4DOP

Input

V1 +

V2 +

V2 +

IN Diag

OUT Diag

IN Diag

OUT Diag

1 V

AUX1

4 IN/OUT

3 V1 –

In/Output

8DXP

I/O

1 V

AUX2

4 IN/OUT

3 V2 –

In/Output

8DXP

I/O

V1 +

V2 +

1

3

2

4

1

3

2

4

Fig. 85: Block diagram – digital modules