USART Operation: SPI Mode

18-5

USART Peripheral Interface, SPI Mode

18.2.2 Master Mode

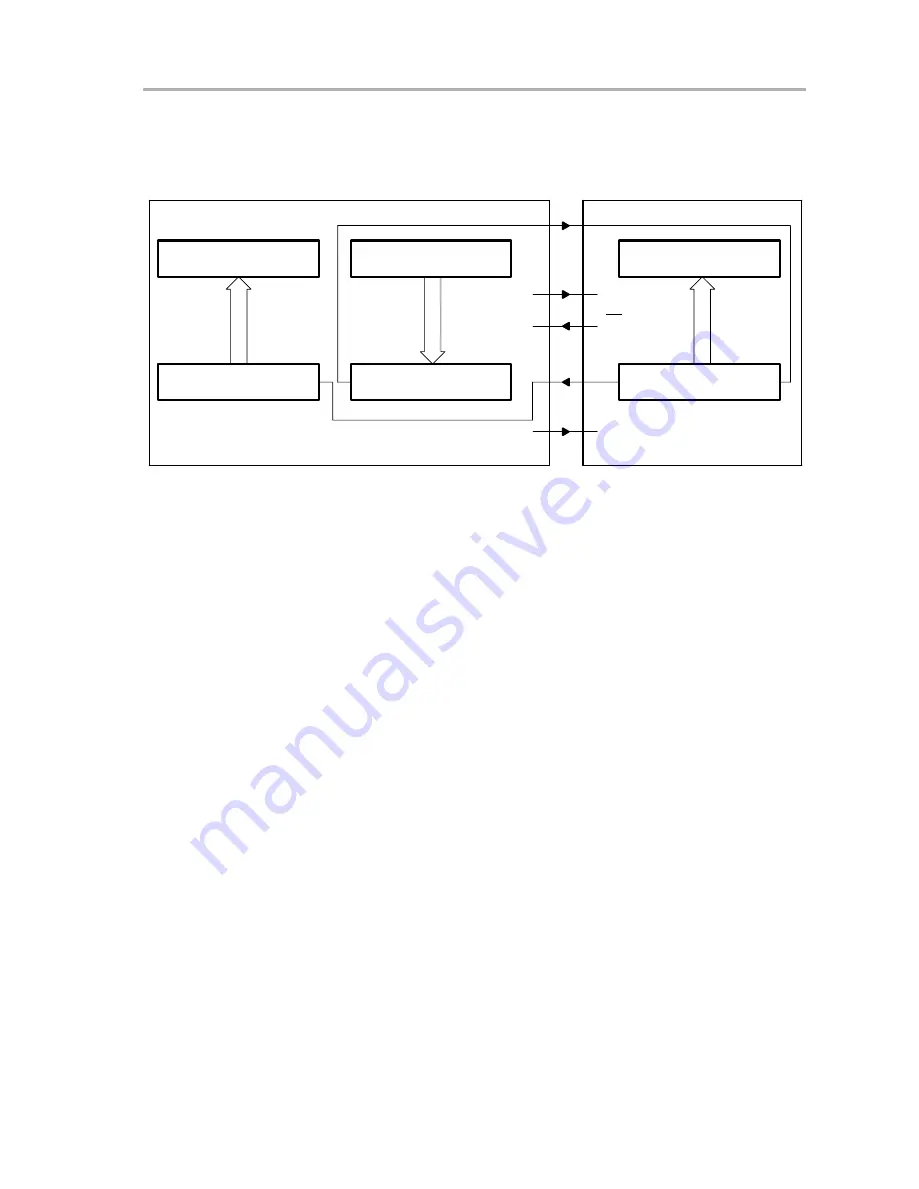

Figure 18−2. USART Master and External Slave

Receive Buffer UxRXBUF

Receive Shift Register

MSB

LSB

Transmit Buffer UxTXBUF

Transmit Shift Register

MSB

LSB

SPI Receive Buffer

Data Shift Register (DSR)

MSB

LSB

SOMI

SOMI

SIMO

SIMO

MASTER

SLAVE

Px.x

STE

STE

SS

Port.x

UCLK

SCLK

MSP430 USART

COMMON SPI

Figure 18−2 shows the USART as a master in both 3-pin and 4-pin

configurations. The USART initiates a data transfer when data is moved to the

transmit data buffer UxTXBUF. The UxTXBUF data is moved to the TX shift

register when the TX shift register is empty, initiating data transfer on SIMO

starting with the most-significant bit. Data on SOMI is shifted into the receive

shift register on the opposite clock edge, starting with the most-significant bit.

When the character is received, the receive data is moved from the RX shift

register to the received data buffer UxRXBUF and the receive interrupt flag,

URXIFGx, is set, indicating the RX/TX operation is complete.

A set transmit interrupt flag, UTXIFGx, indicates that data has moved from

UxTXBUF to the TX shift register and UxTXBUF is ready for new data. It does

not indicate RX/TX completion. In master mode, the completion of an active

transmission is indicated by a set transmitter empty bit TXEPT = 1.

To receive data into the USART in master mode, data must be written to

UxTXBUF because receive and transmit operations operate concurrently.

Four-Pin SPI Master Mode

In 4-pin master mode, STE is used to prevent conflicts with another master.

The master operates normally when STE is high. When STE is low:

-

SIMO and UCLK are set to inputs and no longer drive the bus

-

The error bit FE is set indicating a communication integrity violation to be

handled by the user

A low STE signal does not reset the USART module. The STE input signal is

not used in 3-pin master mode.

Summary of Contents for MSP430x4xx Family

Page 1: ...MSP430x4xx Family 2007 Mixed Signal Products User s Guide SLAU056G ...

Page 2: ......

Page 6: ...vi ...

Page 114: ...3 76 RISC 16 Bit CPU ...

Page 304: ...5 20 FLL Clock Module ...

Page 340: ...7 8 Supply Voltage Supervisor ...

Page 348: ...8 8 16 Bit Hardware Multiplier ...

Page 372: ...9 24 32 Bit Hardware Multiplier ...

Page 400: ...10 28 DMA Controller ...

Page 428: ...13 10 Basic Timer1 ...

Page 466: ...15 24 Timer_A ...

Page 522: ...17 30 USART Peripheral Interface UART Mode ...

Page 544: ...18 22 USART Peripheral Interface SPI Mode ...

Page 672: ...23 12 Comparator_A ...

Page 692: ...24 20 LCD Controller ...

Page 746: ...26 28 ADC12 ...