Timer_A Operation

15-12

Timer_A

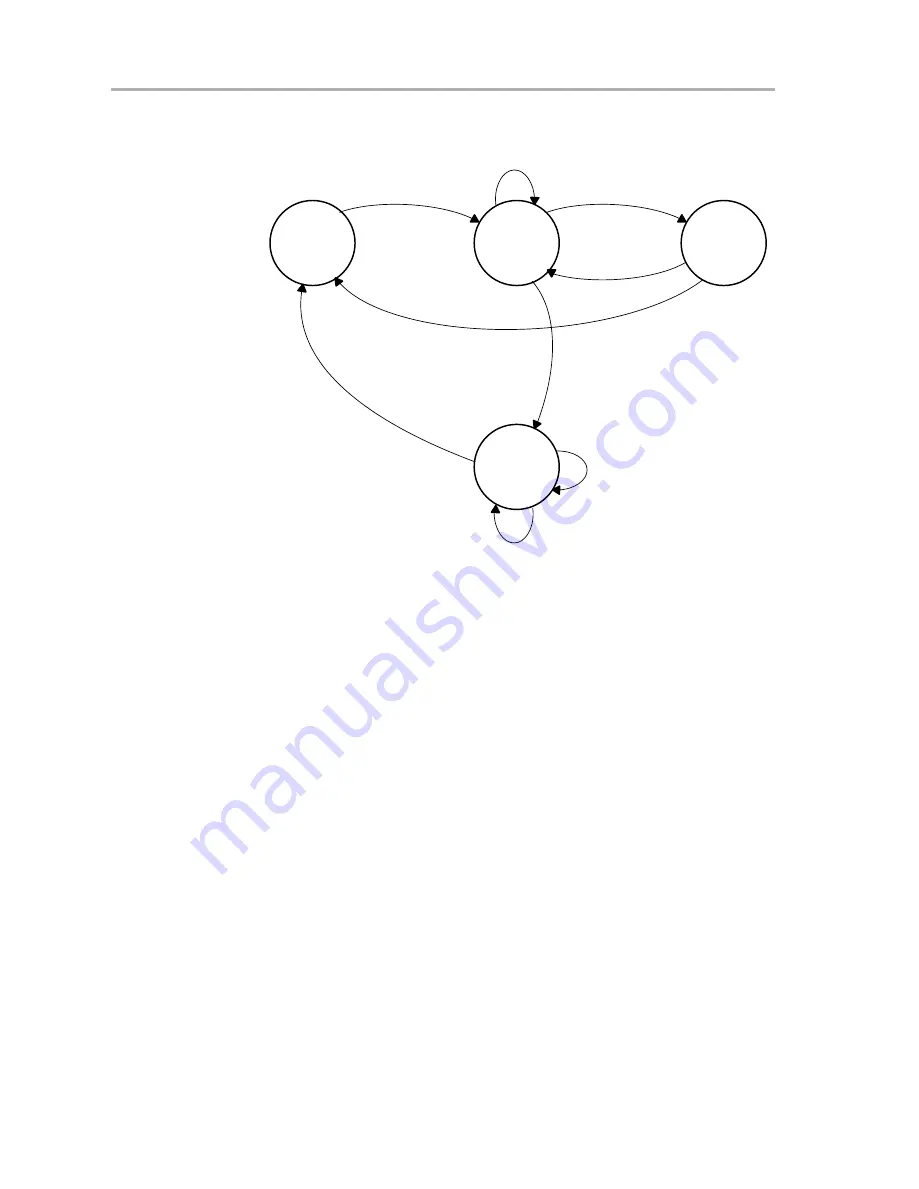

Figure 15−11.Capture Cycle

Second

Capture

Taken

COV = 1

Capture

Taken

No

Capture

Taken

Read

Taken

Capture

Clear Bit COV

in Register TACCTLx

Idle

Idle

Capture

Capture Read and No Capture

Capture

Capture Read

Capture

Capture

Capture Initiated by Software

Captures can be initiated by software. The CMx bits can be set for capture on

both edges. Software then sets CCIS1 = 1 and toggles bit CCIS0 to switch the

capture signal between V

CC

and GND, initiating a capture each time CCIS0

changes state:

MOV

#CAP+SCS+CCIS1+CM_3,&TACCTLx ; Setup TACCTLx

XOR

#CCIS0,&TACCTLx

; TACCTLx = TAR

Compare Mode

The compare mode is selected when CAP = 0. The compare mode is used to

generate PWM output signals or interrupts at specific time intervals. When

TAR counts to the value in a TACCRx:

-

Interrupt flag CCIFG is set

-

Internal signal EQUx = 1

-

EQUx affects the output according to the output mode

-

The input signal CCI is latched into SCCI

Summary of Contents for MSP430x4xx Family

Page 1: ...MSP430x4xx Family 2007 Mixed Signal Products User s Guide SLAU056G ...

Page 2: ......

Page 6: ...vi ...

Page 114: ...3 76 RISC 16 Bit CPU ...

Page 304: ...5 20 FLL Clock Module ...

Page 340: ...7 8 Supply Voltage Supervisor ...

Page 348: ...8 8 16 Bit Hardware Multiplier ...

Page 372: ...9 24 32 Bit Hardware Multiplier ...

Page 400: ...10 28 DMA Controller ...

Page 428: ...13 10 Basic Timer1 ...

Page 466: ...15 24 Timer_A ...

Page 522: ...17 30 USART Peripheral Interface UART Mode ...

Page 544: ...18 22 USART Peripheral Interface SPI Mode ...

Page 672: ...23 12 Comparator_A ...

Page 692: ...24 20 LCD Controller ...

Page 746: ...26 28 ADC12 ...