Theory of Operation—492/492P Service Vol. 1 (SN B030000 & up)

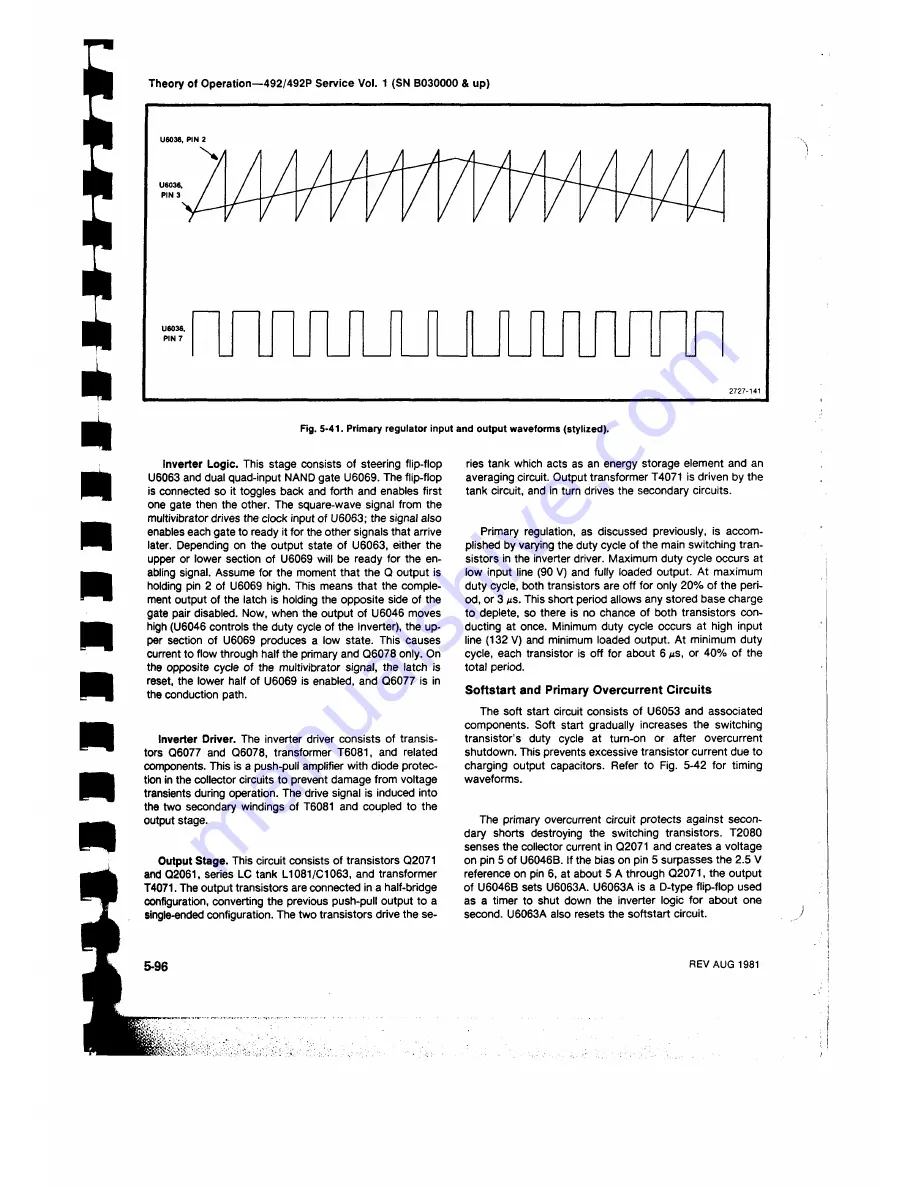

Fig. 5-41. Primary regulator input and output waveforms (stylized).

Inverter

Logic. This stage consists of steering flip-flop

U6063 and dual quad-input NAND gate U6069. The flip-flop

is connected so it toggles back and forth and enables first

one gate then the other. The square-wave signal from the

multivibrator drives the clock input of U6063; the signal also

enables each gate to ready it for the other signals that arrive

later. Depending on the output state of U6063, either the

upper or lower section of U6069 will be ready for the en

abling signal. Assume for the moment that the Q output is

holding pin 2 of U6069 high. This means that the comple

ment output of the latch is holding the opposite side of the

gate pair disabled. Now, when the output of U6046 moves

high (U6046 controls the duty cycle of the Inverter), the up

per section of U6069 produces a low state. This causes

current to flow through half the primary and Q6078 only. On

the opposite cycle of the multivibrator signal, the latch is

reset, the lower half of U6069 is enabled, and Q6077 is in

the conduction path.

Inverter Driver.

The inverter driver consists of transis

tors Q6077 and Q6078, transformer T6081, and related

components. This is a push-pull amplifier with diode protec

tion in the collector circuits to prevent damage from voltage

transients during operation. The drive signal is induced into

the two secondary windings of T6081 and coupled to the

output stage.

Output Stage.

This circuit consists of transistors Q2071

and Q2061, series LC tank L1081/C1063, and transformer

T4071. The output transistors are connected in a half-bridge

configuration, converting the previous push-pull output to a

single-ended configuration. The two transistors drive the se

ries tank which acts as an energy storage element and an

averaging circuit. Output transformer T4071 is driven by the

tank circuit, and in turn drives the secondary circuits.

Primary regulation, as discussed previously, is accom

plished by varying the duty cycle of the main switching tran

sistors in the inverter driver. Maximum duty cycle occurs at

low input line (90 V) and fully loaded output. At maximum

duty cycle, both transistors are off for only

2 0

% of the peri

od, or 3 ms. This short period allows any stored base charge

to deplete, so there is no chance of both transistors con

ducting at once. Minimum duty cycle occurs at high input

line (132 V) and minimum loaded output. At minimum duty

cycle, each transistor is off for about

6

ms, or 40% of the

total period.

Softstart and Primary Overcurrent Circuits

The soft start circuit consists of U6053 and associated

components. Soft start gradually increases the switching

transistor’s duty cycle at turn-on or after overcurrent

shutdown. This prevents excessive transistor current due to

charging output capacitors. Refer to Fig. 5-42 for timing

waveforms.

The primary overcurrent circuit protects against secon

dary shorts destroying the switching transistors. T2080

senses the collector current in Q2071 and creates a voltage

on pin 5 of U6046B. If the bias on pin 5 surpasses the 2.5 V

reference on pin

6

, at about 5 A through Q2071, the output

of U6046B sets U6063A. U6063A is a D-type flip-flop used

as a timer to shut down the inverter logic for about one

second. U6063A also resets the softstart circuit.

5-96

REV AUG 1981