Copyright © Siemens AG 2016. All rights reserved

197

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

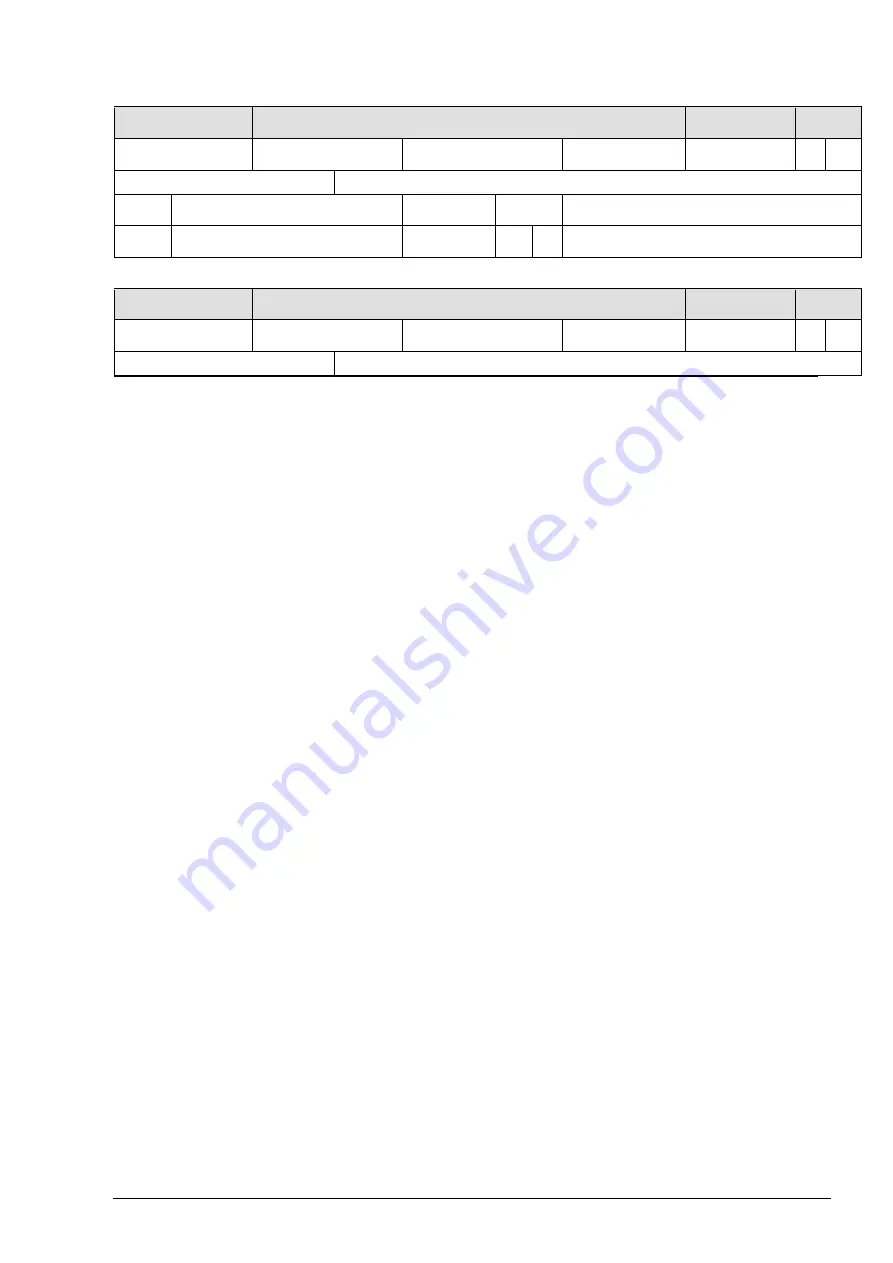

Register:

XHIF_1_P3_CFG

Address:

F8h

Bits:

0dt0

Reset value:

0h

Attributes: r w

Description:

Configuration of the buffering mode for page #3

Bit

Identifier

Reset

Attr.

Function / Description

0

XHIF_1_P3_CFG_BUFMOD 0h

r w 16bit access mode of page #3

Register:

XHIF_1_VERSION

Address:

FCh

Bits:

31dt0

Reset value:

04000804h Attributes: r

Description:

Metal-fix register for XHIF Version

2.3.7 Peripheral Interface

The peripheral interface is operated as passive (i.e. as slave) at the multi-layer AHB and,

in one version, acts as the communication interface between an external application (host

CPU) and the PN stack running internally (ARM-CPU) or the Profinet IP (PN-IP). In an-

other version (application running on an external host), the peripheral interface is used

merely as the interface for consistent data management of the cyclic IO data for the PN-

IP.. The cyclic IO data are also managed consistently by the Consistence Control module

in the peripheral interface. ARM and host interface access to Consistence Control are

multiplexed (arbitrated), as only the internal ARM926 or an external host system requires

access.. As direct access to the IO data is possible from the PN-IP, there are no relevant

lockout times for data transport. The IO data required can therefore be sent straight from

or received directly by the peripheral interface without buffering at the local API (cut-

through).

Consistence-Control ensures the consistency of the IO data saved in the IO-RAM. Con-

sistent storage between the PN-IP (communicative instance) and the ARM, host interface

and data IO interfaces (applicative instances) is realized in the process.

The APB slave IF of the parameter module is used for application-specific configuration

of the peripheral interface by ARM926. Access to the entire memory area is possible over

the APB for initializing the IO RAM. This requires both ready control and byte-by-byte

access with byte enable at the APB. Access to the local IO APB and therefore to the

modules connected to it is possible from the APB slave IF over the data IO interface for

initial configuration.

The mechanisms required for two-way communication between the ARM and host CPU

are implemented in the event unit. The event unit stores event bits which can be set both

by the ARM for the external host system and vice versa. These events cause the module

to trigger an interrupt for the ARM926 interrupt controller (IRQ54: ARM-IRQ, see

2.3.2.14) or the external host system (Host_IRQ = ASIC pin: XHIF_XIRQ). The registers

can be

written and read with common AHB access. The event unit is configured with the parame-

ter module and therefore the APB.