70

CHAPTER 3 CPU

3.7.6

Notes on Standby Mode

Even if the standby control register (STBC) sets standby mode, transition to standby

mode is not allowed when a peripheral function generates an interrupt request. When

an interrupt causes a return from standby mode to active mode, subsequent operations

depend on whether interrupt requests are acceptable.

■

Transition to Standby Mode and Interrupt

When an interrupt request with an interrupt level higher than 11

B

is generated in a peripheral function to

the CPU, an attempt to write "1" into the stop bit (STBC: STP) or sleep bit (SLP) in the standby control

register is ignored. Therefore, any attempt at transition to standby mode fails. (Even after the interrupt is

processed, transition to standby mode is not allowed.)

This type of rejection does not depend on whether the CPU can accept interrupts.

Even if the CPU is processing an interrupt, transition to standby mode is allowed when the request flag bit

for the interrupt has been cleared and there are no other interrupt requests to be processed.

■

Cancellation of Standby Mode by an Interrupt

When an interrupt request with an interrupt level higher than 11

B

is generated in a peripheral function or

another component in sleep mode or stop mode, standby mode is cancelled. This operation does not depend

on whether the CPU can accept interrupts.

After cancellation of standby mode, the CPU normally takes a branch to the interrupt processing routine if

the priority of the interrupt level setting register (ILR1 to ILR4) corresponding to the interrupt request is

higher than the level specified in the interrupt level bits (CCR: IL1 and IL0) in the condition code register

and if the interrupt enable flag is turned on (CCR: I = 1). Otherwise, an instruction is managed following

the instruction causing standby mode to be set.

To prohibit a branch to the interrupt processing routine immediately after return, interrupts must be

prohibited before standby mode is set.

■

Notes on Setting Standby Mode

For setting standby mode using the standby control register (STBC), use the settings specified in Table 3.7-

5 . When 1 is set to both bits at the same time, stop mode has precedence over sleep mode. However, it is

recommended that "1" not be set to the bits at the same time.

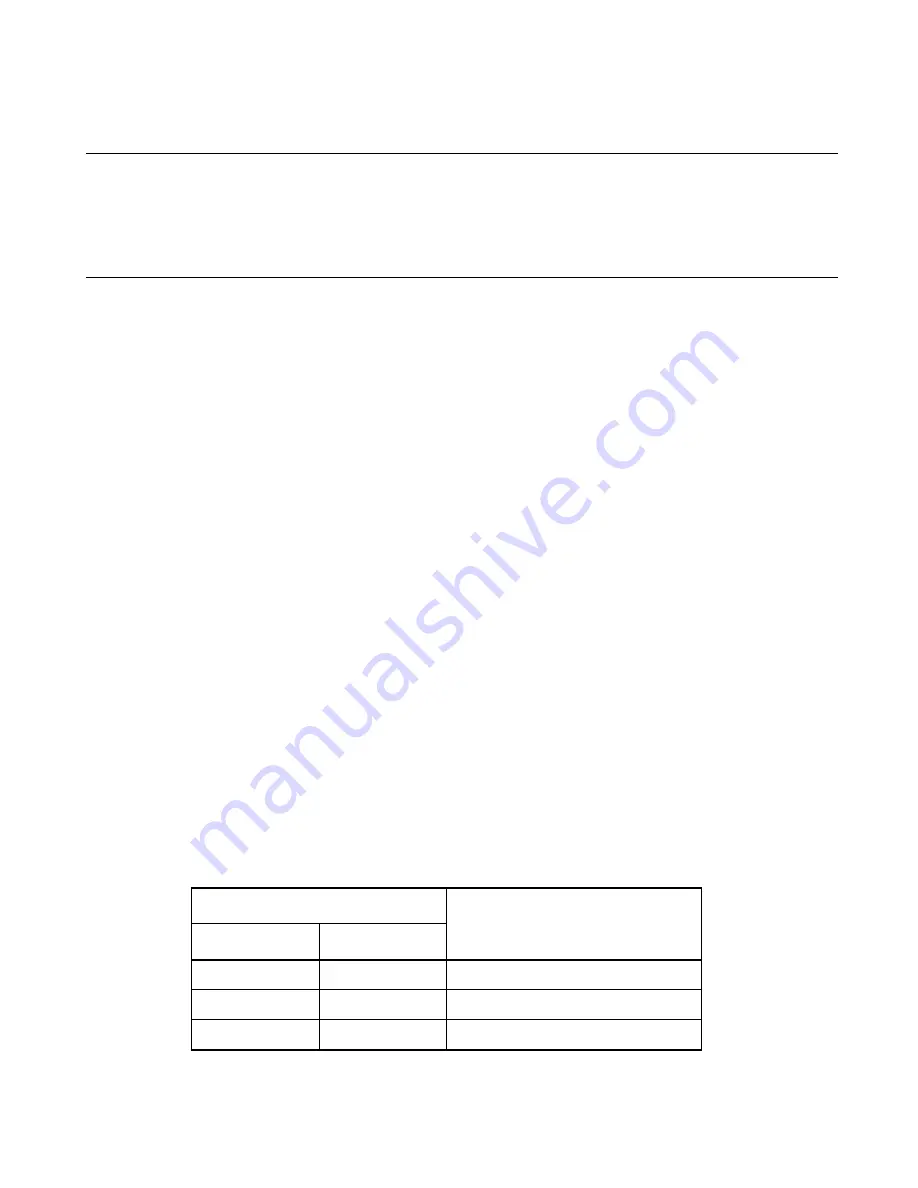

Table 3.7-5 Low-power Consumption Mode Established using the Standby Control

Register (STBC)

STBC register

Mode

STP(bit7)

SLP(bit6)

0

0

Active

0

1

Sleep

1

0

Stop

Summary of Contents for F2MC-8L F202RA

Page 2: ......

Page 4: ......

Page 32: ...16 CHAPTER 1 OVERVIEW ...

Page 90: ...74 CHAPTER 3 CPU ...

Page 142: ...126 CHAPTER 5 TIME BASE TIMER POPW A RETI ENDS END ...

Page 150: ...134 CHAPTER 6 WATCHDOG TIMER ...

Page 176: ...160 CHAPTER 7 8 BIT PWM TIMER ...

Page 220: ...204 CHAPTER 8 8 16 BIT CAPTURE TIMER COUNTER ...

Page 240: ...224 CHAPTER 9 12 BIT PPG TIMER ...

Page 274: ...258 CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT 2 LEVEL ...

Page 362: ...346 CHAPTER 15 BUZZER OUTPUT ...

Page 390: ...374 CHAPTER 17 FLASH MEMORY ...

Page 419: ...403 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Page 434: ...418 INDEX ...

Page 436: ......