RL78/G1P

CHAPTER 5 CLOCK GENERATOR

R01UH0895EJ0100 Rev.1.00

110

Nov 29, 2019

5.3.8 High-speed on-chip oscillator trimming register (HIOTRM)

This register is used to adjust the accuracy of the high-speed on-chip oscillator.

With self-measurement of the high-speed on-chip oscillator frequency via a timer using high-accuracy external clock

input (timer array unit), and so on, the accuracy can be adjusted.

The HIOTRM register can be set by an 8-bit memory manipulation instruction.

Caution The frequency will vary if the temperature and V

DD

pin voltage change after accuracy adjustment.

When the temperature and V

DD

voltage change, accuracy adjustment must be executed regularly or

before the frequency accuracy is required.

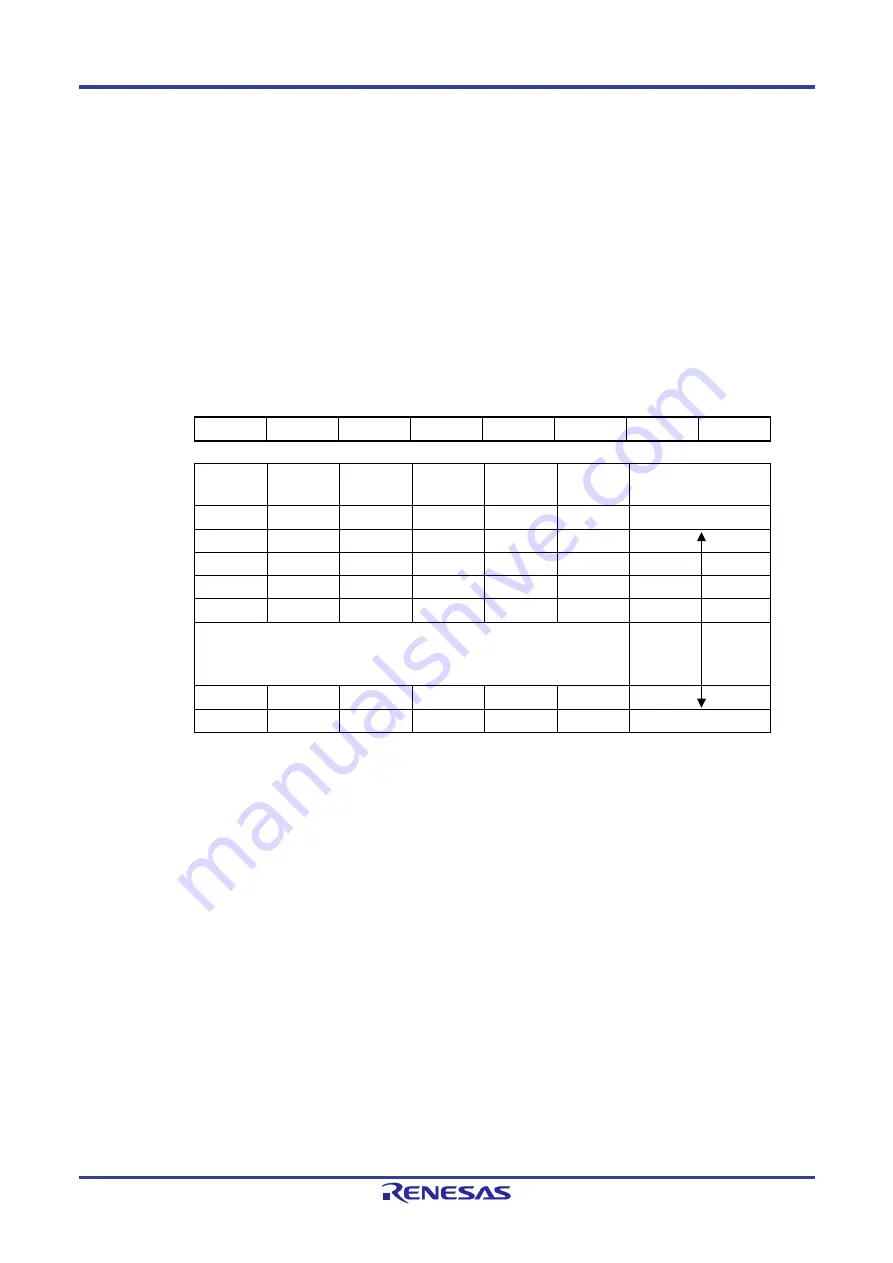

Figure 5-10. Format of High-Speed On-Chip Oscillator Trimming Register (HIOTRM)

Address: F00A0H After reset:

Note

R/W

Symbol

7 6 5 4 3 2 1 0

HIOTRM

0

0

HIOTRM5 HIOTRM4 HIOTRM3 HIOTRM2 HIOTRM1 HIOTRM0

HIOTRM5 HIOTRM4 HIOTRM3 HIOTRM2 HIOTRM1 HIOTRM0 High-speed on-chip

oscillator

0 0 0 0 0 0 Minimum speed

0 0 0 0 0 1

0 0 0 0 1

0

0 0 0 0 1 1

0 0 0 1

0 0

1 1 1 1 1 0

1 1 1 1 1 1

Maximum

speed

Note

The value after reset is adjusted at shipment.

Remarks 1.

The HIOTRM register can be used to adjust the high-speed on-chip oscillator clock to an accuracy

within about 0.05%.

2.

For the usage example of the HIOTRM register, see the application note for RL78 MCU Series High-

speed On-chip Oscillator (HOCO) Clock Frequency Correction (R01AN0464).