Features

11-2

ADSP-214xx SHARC Processor Hardware Reference

Features

The following list describes the IDP features.

• The IDP provides a mechanism for a large number of asynchro-

nous channels (up to eight).

• The IDP supports industry standard data formats, I

2

S, Left-justi-

fied and Right-justified for serial input ports.

• The PDAP supports four data packing modes for parallel data.

• The PDAP supports a maximum of 20-bits.

• Provides two data transfer types, through DMA or interrupt driven

transfer by core.

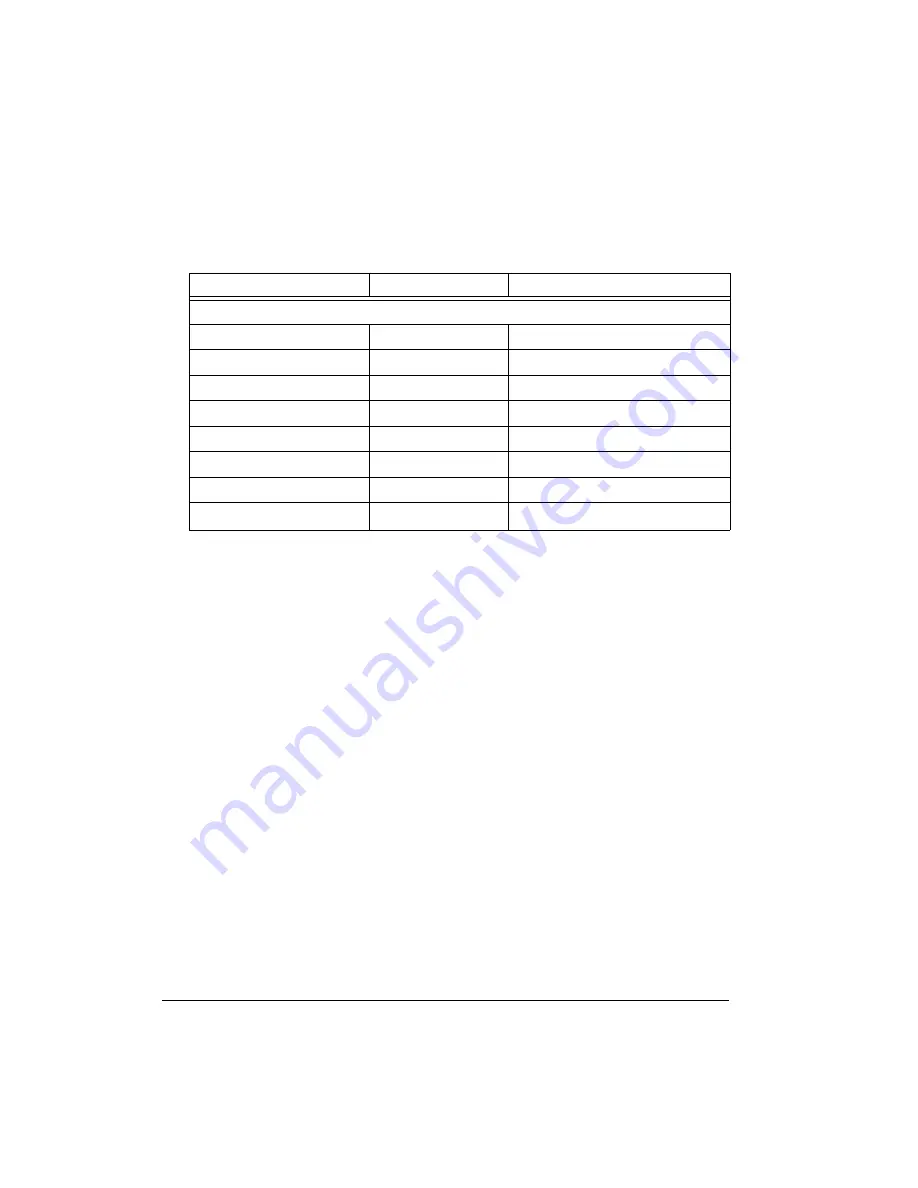

Access Type

Data Buffer

Yes

Yes

Core Data Access

Yes

Yes

DMA Data Access

Yes

Yes

DMA Channels

8

1

DMA Chaining

No

No

Boot Capable

No

No

Local Memory

No

No

Clock Operation

f

PCLK

/4

f

PCLK

/4

Table 11-1. IDP Port Specifications (Cont’d)

Feature

SIP

PDAP

www.BDTIC.com/ADI

Содержание SHARC ADSP-214 Series

Страница 60: ...Contents lx ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 72: ...Notation Conventions lxxii ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 130: ...Programming Model 2 52 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 264: ...Programming Models 3 134 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 290: ...Programming Model 4 26 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 296: ...Programming Model 5 6 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 396: ...Effect Latency 7 28 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 520: ...Programming Model 10 62 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 616: ...Debug Features 14 22 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 656: ...Programming Model 15 40 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 714: ...Programming Model 19 10 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 1132: ...Register Listing A 306 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...

Страница 1192: ...Index I 34 ADSP 214xx SHARC Processor Hardware Reference www BDTIC com ADI...