CXD5602 User Manual

-

736/1010

-

3.9.12.10.275

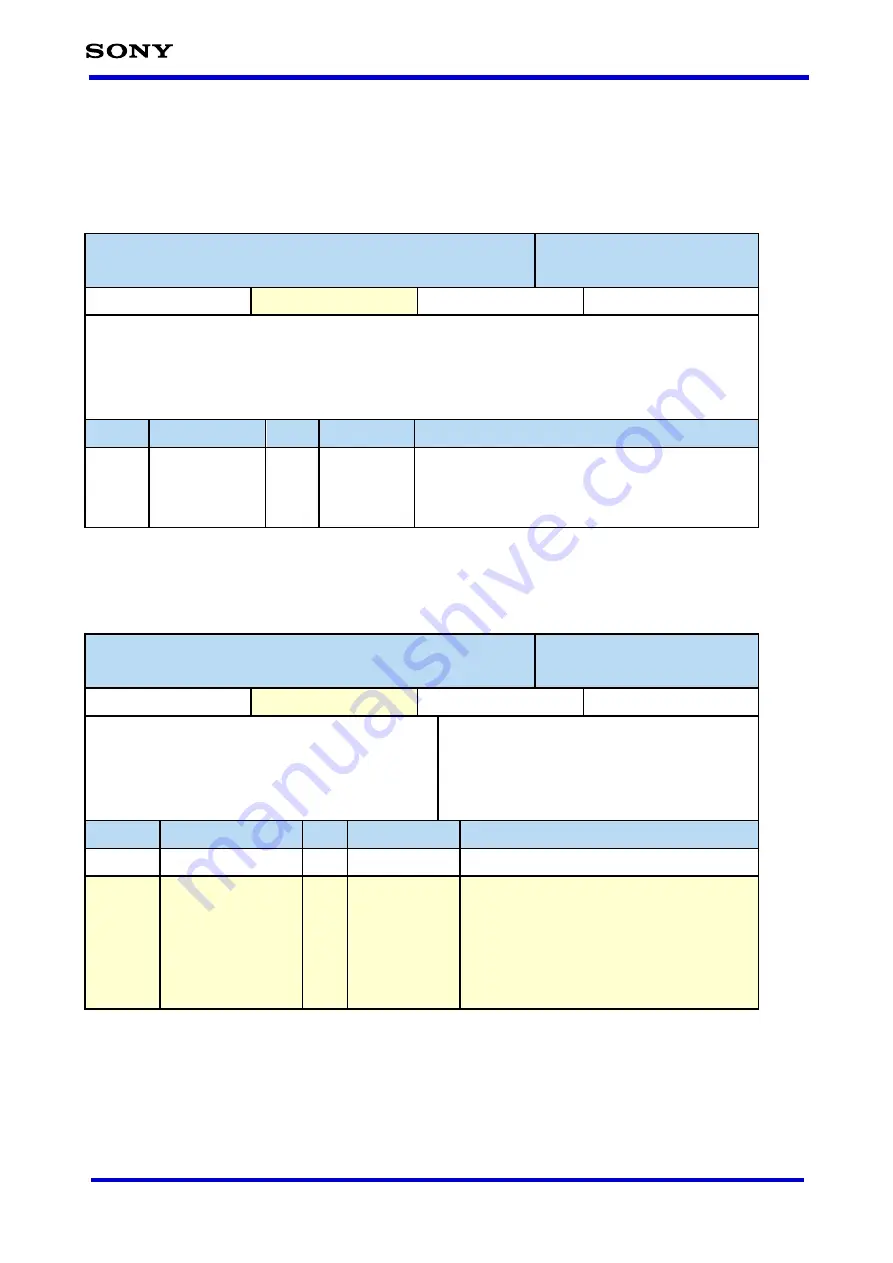

{0x1290} N4_R0_H_TIMSTAMP0 Details

Table SCU (Sensor Control Unit)-604

Local Address: 0x1290

Register Type: RO (read only)

Reset Value: 0x00000000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OLDEST_TIMESTAMP_MSB

Bits

Name

Type

Reset Value

Description

31..0

OLDEST_TIME

STAMP_MSB

RO

0x00000000

Earliest time stamp (integer part of second)

Register for reading out the data in the FIFO

Can read out the earliest data in the FIFO

3.9.12.10.276

{0x1294} N4_R0_H_TIMSTAMP1 Details

Table SCU (Sensor Control Unit)-605

Local Address: 0x1294

Register Type: RO (read only)

Reset Value: 0x00000000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

OLDEST_TIMESTAMP_LSB

Bits

Name

Type Reset Value

Description

31..15

Reserved

RO

0x00000

Reserved

14..0

OLDEST_TIMESTA

MP_LSB

RO

0x0000

Earliest time stamp (second after the decimal

point)

Time stamp supporting the earliest data in the

FIFO

1/32768 second unit

Summary of Contents for CXD5602

Page 1: ...CXD5602 User Manual 1 1010 CXD5602 User Manual ...

Page 36: ...CXD5602 User Manual 36 1010 2 3 Block Diagram Figure Block Diagram 1 CXD5602 Block Diagram ...

Page 144: ...CXD5602 User Manual 144 1010 GNSS_RAMMODE_SEL 0x3F000FFF SRAM GNSS BB 0 5 ON ...

Page 835: ...CXD5602 User Manual 835 1010 enable disable ...