CHAPTER 16 DATA TRANSFER CONTROLLER (DTC)

Page 518 of 920

16.3.1

Allocation of DTC Control Data Area and DTC Vector Table Area

The DTCBAR register is used to set the 256-byte area where DTC control data and the vector table within the

RAM area.

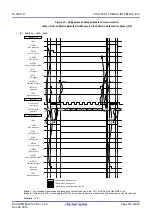

Figure 16 - 2 shows a Memory Map Example when DTCBAR Register is Set to FBH.

In the 192-byte DTC control data area, the space not used by the DTC can be used as RAM.

Figure 16 - 2 Memory Map Example when DTCBAR Register is Set to FBH

The areas where the DTC control data and vector table can be allocated differ depending on the product.

Caution 1. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space as the DTC

control data area or DTC vector table area.

Caution 2. Make sure the stack area, the DTC control data area, and the DTC vector table area do not

overlap.

Caution 3. The internal RAM area in the following products cannot be used as the DTC control data area

or DTC vector table area when using the self-programming and data-flash functions.

R5F11FLL: F3F00H to F4309H

Caution 4. The internal RAM area in the following products cannot be used as the DTC control data area

or DTC vector table area when using the on-chip debugging trace function.

R5F11FLL: F4300H to F46FFH

F3000H

F3F00H

Extended special function

register (2nd SFR)

General-purpose

register

Special function register

(SFR)

Reserved

FFF00H

F0800H

F0000H

FFFFFH

RAM

48 Kbytes

00000H

F1000H

Data flash memory

FFEE0H

Mirror

7FFFFH

Code flash memory

512 Kbytes

Reserved

FFC00H

F

FB

FFH

F

FB

00H

F

FB

40H

DTC control data area

192 bytes

DTC vector table area

40 bytes

Reserved area

24 bytes

DTC used area

256 bytes

Value set in DTCBAR register

F

FB

27H

<R>

Summary of Contents for RL78/G1H

Page 941: ...R01UH0575EJ0120 RL78 G1H...