NUC126

Aug. 08, 2018

Page

736

of 943

Rev 1.03

NUC12

6 S

E

RI

E

S

T

E

CH

NI

CA

L R

E

F

E

RE

NCE

MA

NUA

L

protocol control signal if it is valid for transmission.

Note:

Slave can not define the start itself, but has to react.

The timing of loading data from transmit buffer to data shift unit depends on protocol

configurations.

UART:

A transmission of the data word in transmit buffer can be started if TXEMPTY = 0

in normal operation. In auto flow control, A transmission of the data word in transmit

buffer can be started while TXEMPTY = 0 and USCIx_CTL0 in active stage.

SPI:

In Master mode, data transmission will be started when TXEMPTY

(USCI_BUFSTS[8]) is 0. In Slave mode, the data transmission can be started only when

slave selection signal is at active state and clock is presented on USCIx_CLK pin.

I

2

C:

A transmission of the data byte in transmit buffer can be started if TXEMPTY = 0.

A transmission data which is located in transmit buffer can be started if the TXEMPTY

(USCI_BUFSTS [8]) = 0. The content of the transmit buffer (in TX_BUF condition) should

not be overwritten with new data while it is valid for transmission and a new transmission

can start. If the content of TX_BUF has to be changed, user can set TXRST

(USCI_BUFCTL [16]) to 1 to clear the content of TX_BUF before updating the data.

Moreover, TXEMPTY (USCI_BUFSTS [8]) will be cleared automatically when transmit

buffer (TX_BUF) is updated with new data. While a transmission is in progress, TX_BUF

can be loaded with new data. User has to update the TX_BUF before a new transmission.

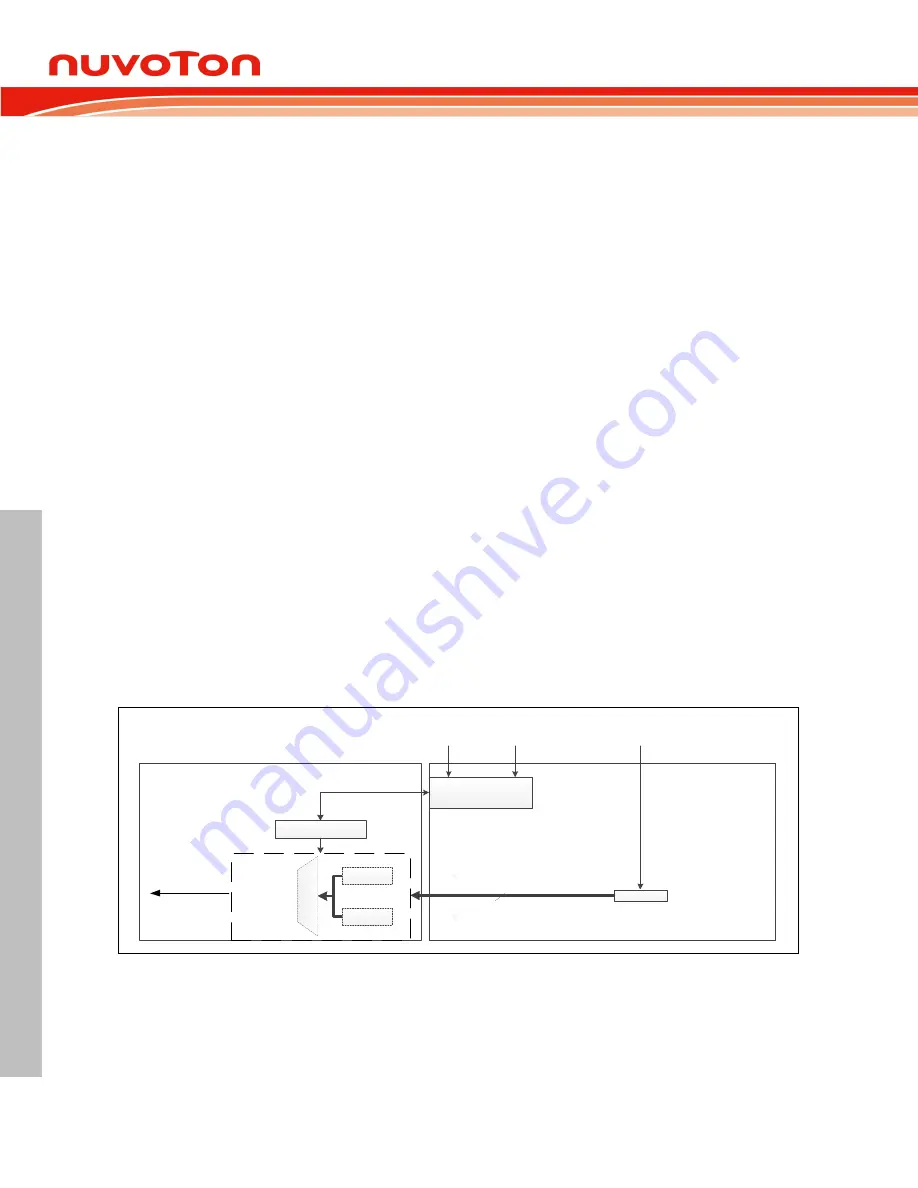

Receive Data Path

The receive data path is based on 16-bit wide receive shift register RX_SFTR and receive buffers

RX_BUF0 and RX_BUF1. The data transfer parameters like data word length, or the shift direction are

controlled commonly for transmission and reception by the line control register USCI_LINECTL.

Register USCI_BUFSTS monitors the data validation of USCI_RXDAT.

Receive Buffering

The receive shift register cannot be directly accessed by user, but its content is automatically loaded

into the receive buffer if a complete data word has been received or the frame is finished. The received

data words in Receive Buffer can be read out automatically from register USCI_RXDAT.

USCI_LINECTL

Shift Control

& Status

Serial Bus

Clock Input

Control

Input

Shift Data

Input

RX_BUF0

RX_BUF1

Control

16

RX_SFTR

Data

Receive Buffer

USCI_RXDAT

Figure 6.19-7 Receive Data Path

6.19.4.3 Port Direction Control

In SPI protocol with half-duplex configurations, the data port is bidirectional. Port direction control is

intended to control the pin direction through a dedicated hardware interface.

The direction of selected pin is controlled by PORTDIR (USCI_TXDAT[16]). When user writes

USCI_TXDAT register, the transmit data and its port direction are settled simultaneously.