NUC126

Aug. 08, 2018

Page

278

of 943

Rev 1.03

NUC12

6 S

E

RI

E

S

T

E

CH

NI

CA

L R

E

F

E

RE

NCE

MA

NUA

L

where V

plus

is the analog input; V

minus

is the inverted analog input.

The V

plus

of differential input paired channel x is from ADC0_CHy pin; V

minus

is from

ADC0_CHz pin, x=0,1..9, y=2*x, z=y+1.

0 = Single-end analog input mode.

1 = Differential analog input mode.

Note:

In Differential Input mode, only the even number of the two corresponding

channels needs to be enabled in ADCHER register. The conversion result will be

placed to the corresponding data register of the enabled channel.

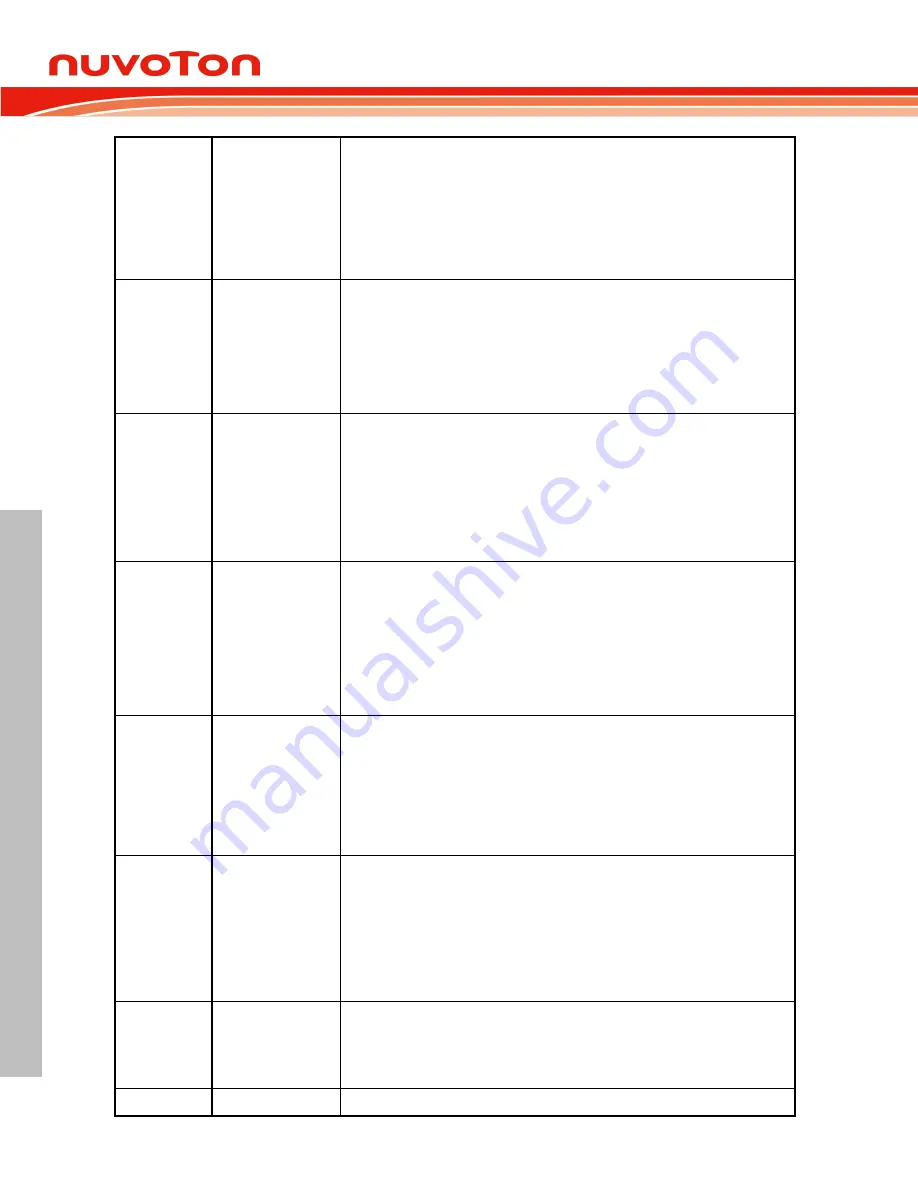

[9]

PTEN

PDMA Transfer Enable Bit

When A/D conversion is completed, the converted data is loaded into ADDR0~19,

ADDR29~ADDR31. Software can enable this bit to generate a PDMA data transfer

request.

0 = PDMA data transfer Disabled.

1 = PDMA data transfer in ADDR0~19, ADDR29~ADDR31 Enabled.

Note:

When PTEN=1, software must set ADIE=0 to disable interrupt.

[8]

TRGEN

External Trigger Enable Bit

Enable or disable triggering of A/D conversion by external STADC pin, PWM trigger

and Timer trigger. If external trigger is enabled, the ADST bit can be set to 1 by the

selected hardware trigger source.

0 = External trigger Disabled.

1 = External trigger Enabled.

Note:

The ADC external trigger function is only supported in Single-cycle Scan

mode.

[7:6]

TRGCOND

External Trigger Condition

These two bits decide external pin STADC trigger event is level or edge. The signal

must be kept at stable state at least 8 PCLKs for level trigger and at least 4 PCLKs

for edge trigger.

00 = Low level.

01 = High level.

10 = Falling edge.

11 = Rising edge.

[5:4]

TRGS

Hardware Trigger Source

00 = A/D conversion is started by external STADC pin.

01 = Timer0 ~ Timer3 overflow pulse trigger.

10 = Reserved.

11 = A/D conversion is started by PWM trigger.

Note:

Software should clear TRGEN bit and ADST bit to 0 before changing TRGS

bits.

[3:2]

ADMD

A/D Converter Operation Mode Control

00 = Single conversion.

01 = Burst conversion.

10 = Single-cycle Scan.

11 = Continuous Scan.

Note1:

When changing the operation mode, software should clear ADST bit first.

Note2:

In Burst mode, the A/D result data is always at ADC Data Register 0.

[1]

ADIE

A/D Interrupt Enable Bit

A/D conversion end interrupt request is generated if ADIE bit is set to 1.

0 = A/D interrupt function Disabled.

1 = A/D interrupt function Enabled.

[0]

ADEN

A/D Converter Enable Bit