System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-12

ID021414

Non-Confidential

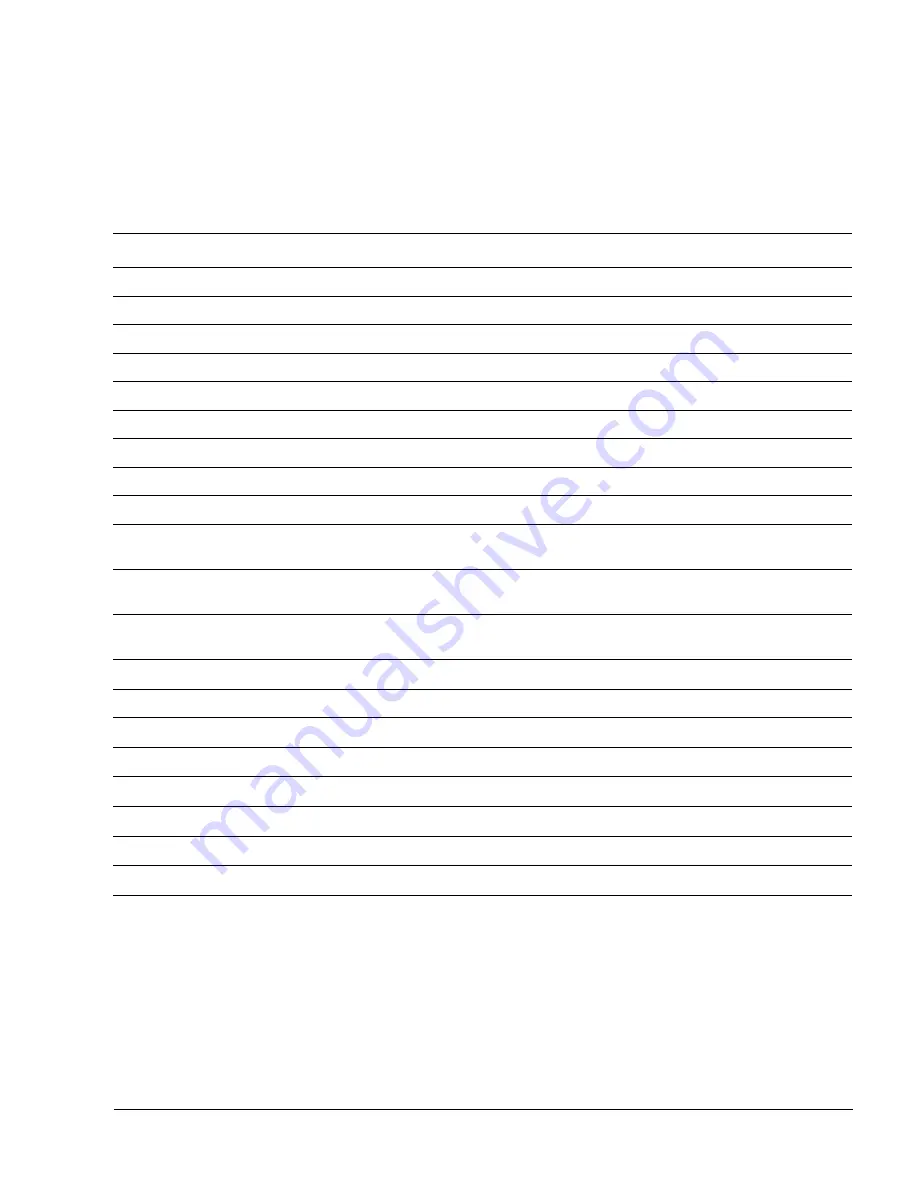

4.2.12

AArch64 implementation defined registers

Table 4-11

shows the

IMPLEMENTATION

DEFINED

registers in AArch64 state. These registers

provide test features and any required configuration options specific to the Cortex-A53

processor. If a register is not indicated as mapped to an AArch32 64-bit register, bits[63:32] are

0x00000000

.

Table 4-11 AArch64 implementation defined registers

Name

Type

Reset

Width

Description

ACTLR_EL1

RW

0x00000000

32

Auxiliary Control Register, EL1

on page 4-55

ACTLR_EL2

RW

0x00000000

32

Auxiliary Control Register, EL2

on page 4-55

ACTLR_EL3

RW

0x00000000

32

Auxiliary Control Register, EL3

on page 4-56

AFSR0_EL1

RW

0x00000000

32

Auxiliary Fault Status Register 0, EL1, EL2 and EL3

on page 4-97

AFSR1_EL1

RW

0x00000000

32

Auxiliary Fault Status Register 1, EL1, EL2 and EL3

on page 4-97

AFSR0_EL2

RW

0x00000000

32

Auxiliary Fault Status Register 0, EL1, EL2 and EL3

on page 4-97

AFSR1_EL2

RW

0x00000000

32

Auxiliary Fault Status Register 1, EL1, EL2 and EL3

on page 4-97

AFSR0_EL3

RW

0x00000000

32

Auxiliary Fault Status Register 0, EL1, EL2 and EL3

on page 4-97

AFSR1_EL3

RW

0x00000000

32

Auxiliary Fault Status Register 1, EL1, EL2 and EL3

on page 4-97

AMAIR_EL1

RW

0x00000000

64

Auxiliary Memory Attribute Indirection Register, EL1, EL2 and

EL3

on page 4-97

AMAIR_EL2

RW

0x00000000

64

Auxiliary Memory Attribute Indirection Register, EL1, EL2 and

EL3

on page 4-97

AMAIR_EL3

RW

0x00000000

64

Auxiliary Memory Attribute Indirection Register, EL1, EL2 and

EL3

on page 4-97

L2CTLR_EL1

RW

-

a

32

L2 Control Register

on page 4-106

L2ECTLR_EL1

RW

0x00000000

32

L2 Extended Control Register

on page 4-107

L2ACTLR_EL1

RW

0x80000000

b

32

L2 Auxiliary Control Register

on page 4-109

CPUACTLR_EL1

c

RW

0x00000000004C8000

64

CPU Auxiliary Control Register, EL1

on page 4-124

CPUECTLR_EL1

c

RW

0x0000000000000000

64

CPU Extended Control Register, EL1

on page 4-128

CPUMERRSR_EL1

c

RW

-

64

CPU Memory Error Syndrome Register

on page 4-129

L2MERRSR_EL1

c

RW

-

64

L2 Memory Error Syndrome Register

on page 4-132

CBAR_EL1

RO

-

d

64

Configuration Base Address Register, EL1

on page 4-134

a. The reset value depends on the processor implementation and the state of the

L2RSTDISABLE

signal.

b. This is the reset value for an ACE interface. For a CHI interface the reset value is

0x80004008

.

c. Mapped to a 64-bit AArch32 register.

d. The reset value depends on the

PERIPHBASE

signal.