System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-15

ID021414

Non-Confidential

To access the MIDR_EL1:

MRS <Xt>, MIDR_EL1 ; Read MIDR_EL1 into Xt

Table 4-14

shows the register access encoding:

The MIDR_EL1 can be accessed through the memory-mapped interface and the external debug

interface, offset

0xD00

.

4.3.2

Multiprocessor Affinity Register

The MPIDR_EL1 characteristics are:

Purpose

Provides an additional core identification mechanism for scheduling

purposes in a cluster system.

Usage constraints

This register is accessible as follows:

Configurations

The MPIDR_EL1[31:0] is:

•

Architecturally mapped to the AArch32 MPIDR register. See

Multiprocessor Affinity Register

on page 4-158

.

•

Mapped to external EDDEVAFF0 register.

MPIDR_EL1[63:32] is mapped to external EDDEVAFF1 register.

Attributes

MPIDR_EL1 is a 64-bit register.

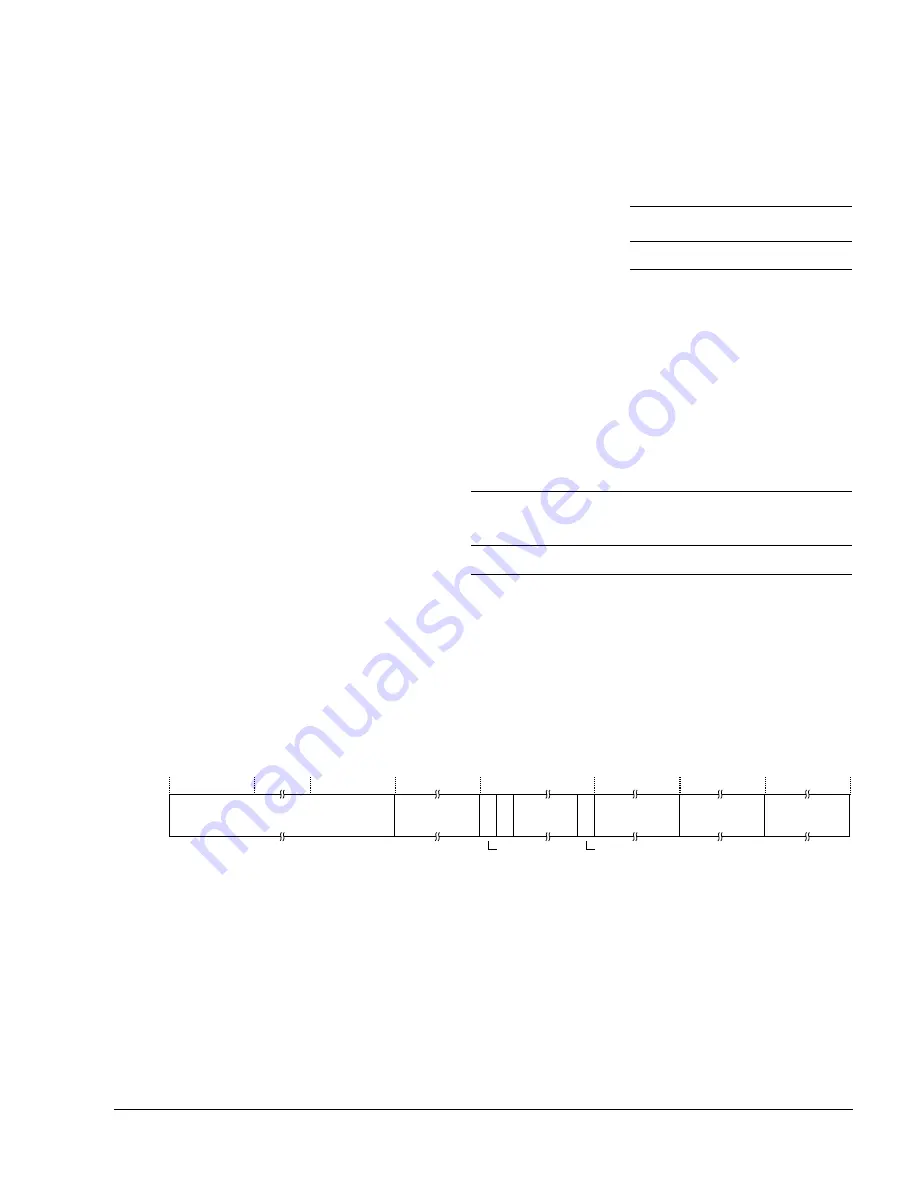

Figure 4-2

shows the MPIDR_EL1 bit assignments.

Figure 4-2 MPIDR_EL1 bit assignments

Table 4-14 MIDR_EL1 access encoding

op0

op1

CRn

CRm

op2

11

000

0000

0000

000

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RO

RO

RO

RO

RO

Aff1

Aff0

0

63

16 15

8 7

Aff2

23

24

MT

RES

0

29

30

U

32 31

Aff3

40 39

RES

0

RES

1