Functional Description

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

2-12

ID021414

Non-Confidential

•

If there are any physical effects that could occur while changing the clock frequency,

ARM recommends that the clock ratio is changed only while the

STANDBYWFIL2

output of the processor is asserted.

•

The input signal

SCLKEN

exists in the Cortex-A53 processor if it is configured to

include the CHI interface.

ATCLKEN

The ATB interface is a synchronous interface that can operate at any integer multiple that is

equal to or slower than the main processor clock,

CLKIN

, using the

ATCLKEN

signal. For

example, the

CLKIN

to

ATCLK

frequency ratio can be 1:1, 2:1, or 3:1, where

ATCLK

is the

ATB bus clock.

ATCLKEN

asserts one

CLKIN

cycle before the rising edge of

ATCLK

. If you

change the

CLKIN

to

ATCLK

frequency ratio, you must change

ATCLKEN

correspondingly.

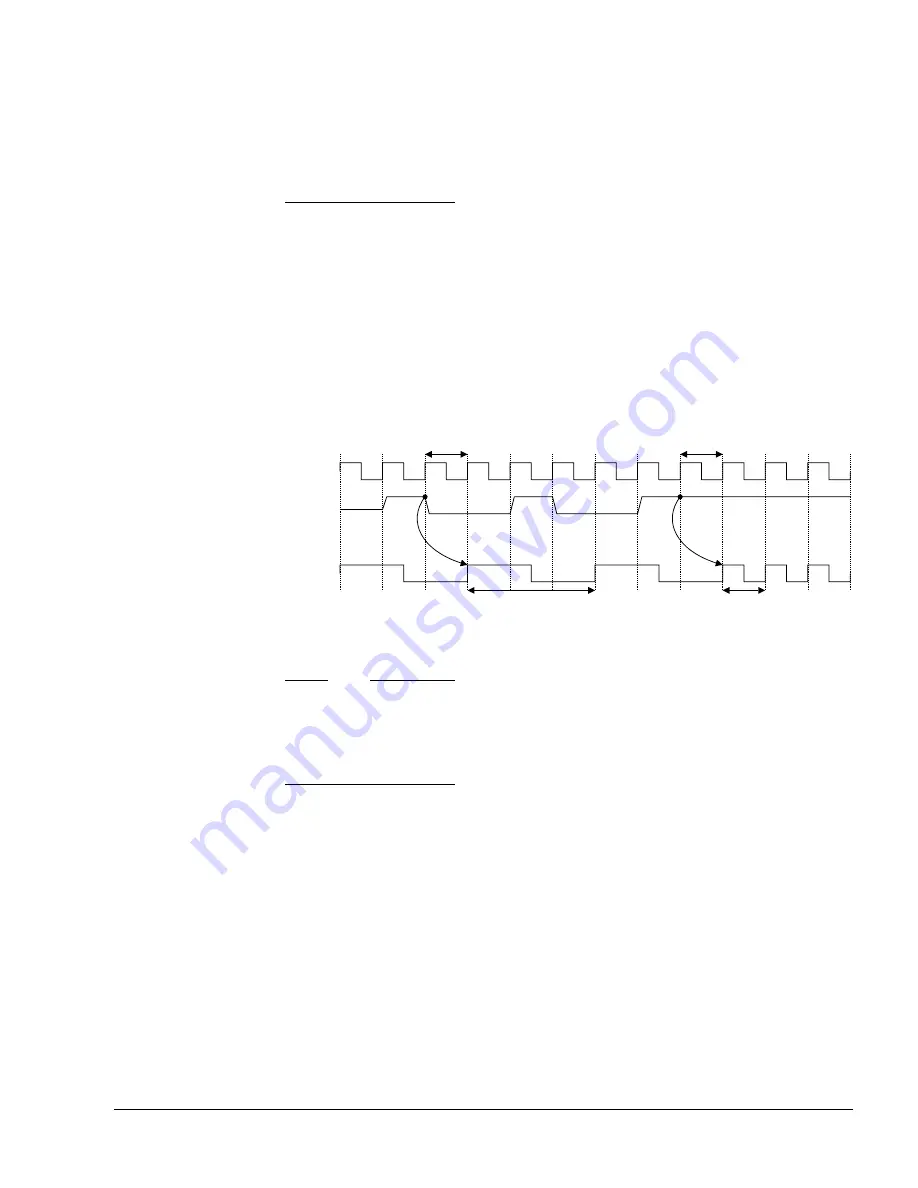

Figure 2-6

shows a timing example of

ATCLKEN

that changes the

CLKIN

to

ATCLK

frequency ratio from 3:1 to 1:1.

Figure 2-6 ATCLKEN with CLKIN:ATCLK ratio changing from 3:1 to 1:1

Note

Figure 2-6

shows the timing relationship between the ATB clock,

ATCLK

and

ATCLKENDBG

, where

ATCLKENDBG

asserts one clock cycle before the rising edge of

ATCLK

. It is important that the relationship between

ATCLK

and

ATCLKENDBG

is

maintained.

CNTCLKEN

The

CNTVALUEB

is a synchronous 64-bit binary encoded counter value that can operate at

any integer multiple that is equal to or slower than the main processor clock,

CLKIN

, using the

CNTCLKEN

signal. For example, you can set the

CLKIN

to

CNTCLK

frequency ratio to 1:1,

2:1, or 3:1, where

CNTCLK

is the system counter clock.

CNTCLKEN

asserts one

CLKIN

cycle prior to the rising edge of

CNTCLK

.

Figure 2-7 on page 2-13

shows a timing example of

CNTCLKEN

that changes the

CLKIN

to

CNTCLK

frequency ratio from 3:1 to 1:1.

ATCLK

ATCLKEN

asserts one

CLKIN

cycle before the rising edge of

ATCLK

1

CLKIN

cycle

CLKIN

:

ATCLK

= 3:1

CLKIN

:

ATCLK

= 1:1

ATCLKEN

CLKIN

1

CLKIN

cycle