System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-38

ID021414

Non-Confidential

Configurations

ID_AA64PFR0_EL1 is architecturally mapped to external register

ID_AA64PFR0_EL1.

Attributes

ID_AA64PFR0_EL1 is a 64-bit register.

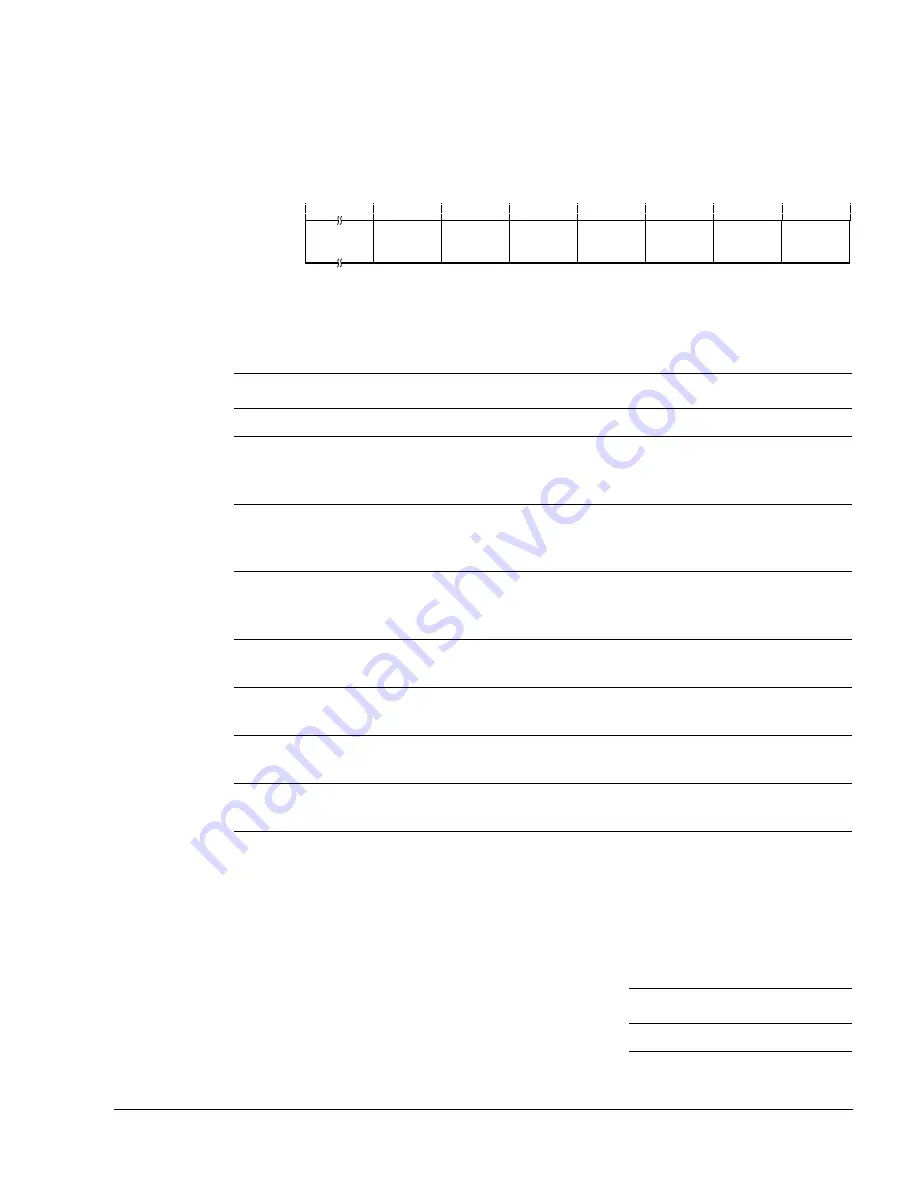

Figure 4-17

shows the ID_AA64PFR0_EL1 bit assignments.

Figure 4-17 ID_AA64PFR0_EL1 bit assignments

Table 4-45

shows the ID_AA64PFR0_EL1 bit assignments.

To access the ID_AA64PFR0_EL1:

MRS <Xt>, ID_AA64PFR0_EL1 ; Read ID_AA64PFR0_EL1 into Xt

Register access is encoded as follows:

63

0

RES

0

4 3

8 7

12 11

16 15

EL3

handling

EL2

handling

EL1

handling

EL0

handling

AdvSIMD

FP

20 19

24 23

GIC

28 27

Table 4-45 ID_AA64PFR0_EL1 bit assignments

Bits

Name

Function

[63:28]

-

Reserved,

RES

0.

[27:24]

GIC

GIC CPU interface:

0x0

GIC CPU interface is disabled.

0x1

GIC CPU interface is implemented.

[23:20]

FP

a

Floating-point. The possible values are:

0x0

Floating-point is implemented.

0xF

Floating-point is not implemented.

[19:16]

AdvSIMD

a

Advanced SIMD. The possible values are:

0x0

Advanced SIMD is implemented.

0xF

Advanced SIMD is not implemented.

[15:12]

EL3 handling

EL3 exception handling:

0x2

Instructions can be executed at EL3 in AArch64 or AArch32 state.

[11:8]

EL2 handling

EL2 exception handling:

0x2

Instructions can be executed at EL2 in AArch64 or AArch32 state.

[7:4]

EL1 handling

EL1 exception handling. The possible values are:

0x2

Instructions can be executed at EL1 in AArch64 or AArch32 state.

[3:0]

EL0 handling

EL0 exception handling. The possible values are:

0x2

Instructions can be executed at EL0 in AArch64 or AArch32 state.

a. The FP and AdvSIMD both take the same value, as both must be implemented, or neither.

Table 4-46 ID_AA64PFR0_EL1 access encoding

op0

op1

CRn

CRm

op2

11

000

0000

0100

000