System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-229

ID021414

Non-Confidential

Write access to the Secure copy of TTBCR is disabled if the

CP15SDISABLE

signal is asserted HIGH.

Attributes

TTBCR is a 32-bit register.

There are two formats for this register. TTBCR.EAE determines which format of the register is

used. This section describes:

•

TTBCR format when using the Short-descriptor translation table format

.

•

TTBCR format when using the Long-descriptor translation table format

.

TTBCR format when using the Short-descriptor translation table format

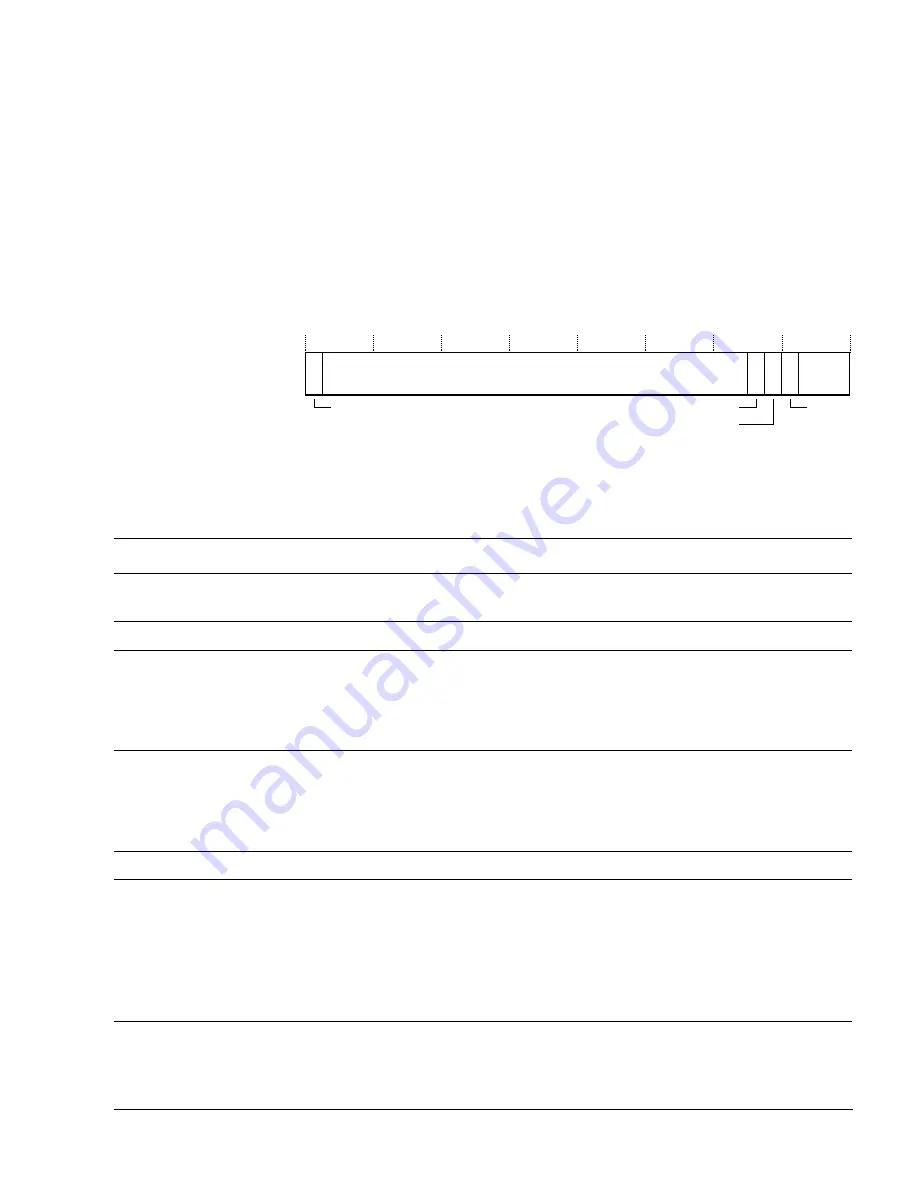

Figure 4-115

shows the TTBCR bit assignments when TTBCR.EAE is 0.

Figure 4-115 TTBCR bit assignments, TTBCR.EAE is 0

Table 4-210

shows the TTBCR bit assignments when TTBCR.EAE is 0.

TTBCR format when using the Long-descriptor translation table format

Figure 4-116 on page 4-230

shows the TTBCR bit assignments when TTBCR.EAE is 1.

31 30

6 5 4 3 2

0

N

RES

0

PD1

EAE

PD0

RES

0

Table 4-210 TTBCR bit assignments, TTBCR.EAE is 0

Bits

Name

Function

[31]

EAE

Extended Address Enable.

0

Use the 32-bit translation system, with the Short-descriptor translation table format.

[30:6]

-

Reserved,

RES

0.

[5]

PD1

Translation table walk disable for translations using TTBR1. This bit controls whether a translation table walk is

performed on a TLB miss, for an address that is translated using TTBR1. The possible values are:

0

Perform translation table walks using TTBR1.

1

A TLB miss on an address that is translated using TTBR1 generates a Translation fault. No

translation table walk is performed.

[4]

PD0

Translation table walk disable for translations using TTBR0. This bit controls whether a translation table walk is

performed on a TLB miss for an address that is translated using TTBR0. The possible values are:

0

Perform translation table walks using TTBR0.

1

A TLB miss on an address that is translated using TTBR0 generates a Translation fault. No

translation table walk is performed.

[3]

-

Reserved,

RES

0.

[2:0]

N

Indicate the width of the base address held in TTBR0. In TTBR0, the base address field is bits[31:14-N]. The value

of N also determines:

•

Whether TTBR0 or TTBR1 is used as the base address for translation table walks.

•

The size of the translation table pointed to by TTBR0.

N can take any value from 0 to 7, that is, from 0b000 to 0b111.

When N has its reset value of 0, the translation table base is compatible with ARMv5 and ARMv6.

Resets to 0.