System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-154

ID021414

Non-Confidential

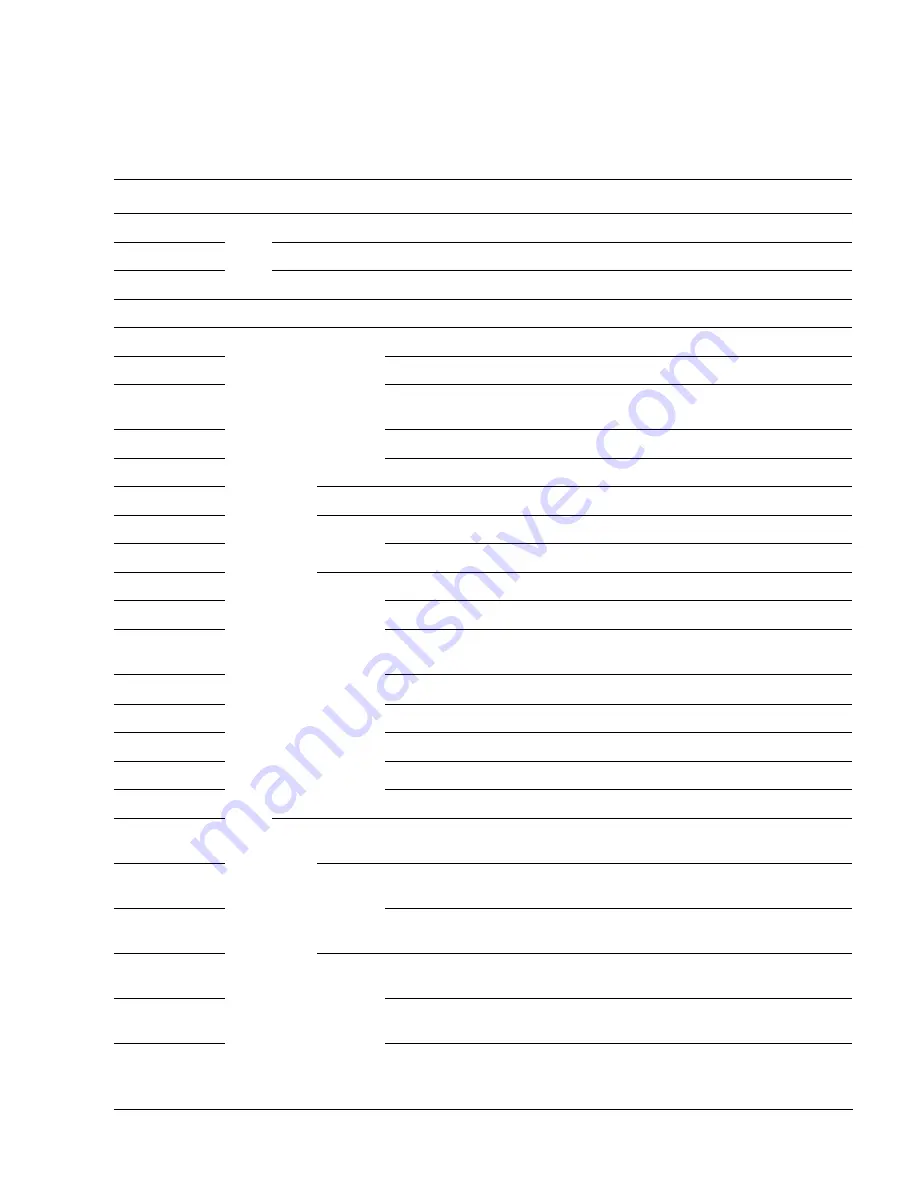

4.4.26

AArch32 GIC system registers

Table 4-146

shows the GIC system registers in AArch32 state.

Table 4-146 AArch32 GIC system registers

Name

CRn

Op1

CRm

Op2

Type

Reset Width

Description

ICC_SGI1R

-

0

c12

-

WO

-

64-bit

SGI Generation Register 1

ICC_ASGI1R

1

c12

-

WO

-

64-bit

Alternate SGI Generation Register 1

ICC_SGI0R

2

c12

-

WO

-

64-bit

SGI Generation Register 0

ICC_PMR

c4

0

c6

0

RW

0x00000000

32-bit

Priority Mask Register

ICC_IAR0

c12

0

c8

0

RO

-

32-bit

Interrupt Acknowledge Register 0

ICC_EOIR0

1

WO

-

32-bit

End Of Interrupt Register 0

ICC_HPPIR0

2

RO

-

32-bit

Highest Priority Pending Interrupt

Register 0

ICC_BPR0

3

RW

0x00000002

32-bit

Binary Point Register 0

ICC_AP0R0

4

RW

0x00000000

32-bit

Active Priorities 0 Register 0

ICC_AP1R0

c9

0

RW

0x00000000

32-bit

Active Priorities 1 Register 0

ICC_DIR

c11

1

WO

-

32-bit

Deactivate Interrupt Register

ICC_RPR

3

RO

-

32-bit

Running Priority Register

ICC_IAR1

c12

0

RO

-

32-bit

Interrupt Acknowledge Register 1

ICC_EOIR1

1

WO

-

32-bit

End Of Interrupt Register 1

ICC_HPPIR1

2

RO

-

32-bit

Highest Priority Pending Interrupt

Register 1

ICC_BPR1

3

RW

0x00000003

a

32-bit

Binary Point Register 1

ICC_CTLR

4

RW

0x00000400

32-bit

Interrupt Control Register

ICC_SRE

5

RW

0x00000000

32-bit

System Register Enable Register

ICC_IGRPEN0

6

RW

0x00000000

32-bit

Interrupt Group Enable Register 0

ICC_IGRPEN1

7

RW

0x00000000

32-bit

Interrupt Group Enable Register 1

ICH_AP0R0

4

c8

0

RW

0x00000000

32-bit

Interrupt Controller Hyp Active

Priorities Register (0,0)

ICH_AP1R0

c9

0

RW

0x00000000

32-bit

Interrupt Controller Hyp Active

Priorities Register (1,0)

ICC_HSRE

5

RW

0x00000000

32-bit

System Register Enable Register for

EL2

ICH_HCR

c11

0

RW

0x00000000

32-bit

Interrupt Controller Hyp Control

Register

ICH_VTR

1

RO

0x90000003

32-bit

Interrupt Controller VGIC Type

Register

ICH_MISR

2

RO

0x00000000

32-bit

Interrupt Controller Maintenance

Interrupt State Register