System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-199

ID021414

Non-Confidential

To access the CPACR:

MRC p15,0,<Rt>,c1,c0,2 ; Read CPACR into Rt

MCR p15,0,<Rt>,c1,c0,2 ; Write Rt to CPACR

4.5.30

Secure Configuration Register

The SCR characteristics are:

Purpose

Defines the configuration of the current security state. It specifies:

•

The security state of the processor, Secure or Non-secure.

•

What state the processor branches to, if an IRQ, FIQ or external

abort occurs.

•

Whether the CPSR.F and CPSR.A bits can be modified when

SCR.NS = 1.

Usage constraints

This register is accessible as follows:

Any read or write to SCR in Secure EL1 state in AArch32 is trapped as an

exception to EL3.

Configurations

The SCR is a Restricted access register that exists only in the Secure state.

The SCR is mapped to the AArch64 SCR_EL3 register.

Attributes

SCR is a 32-bit register.

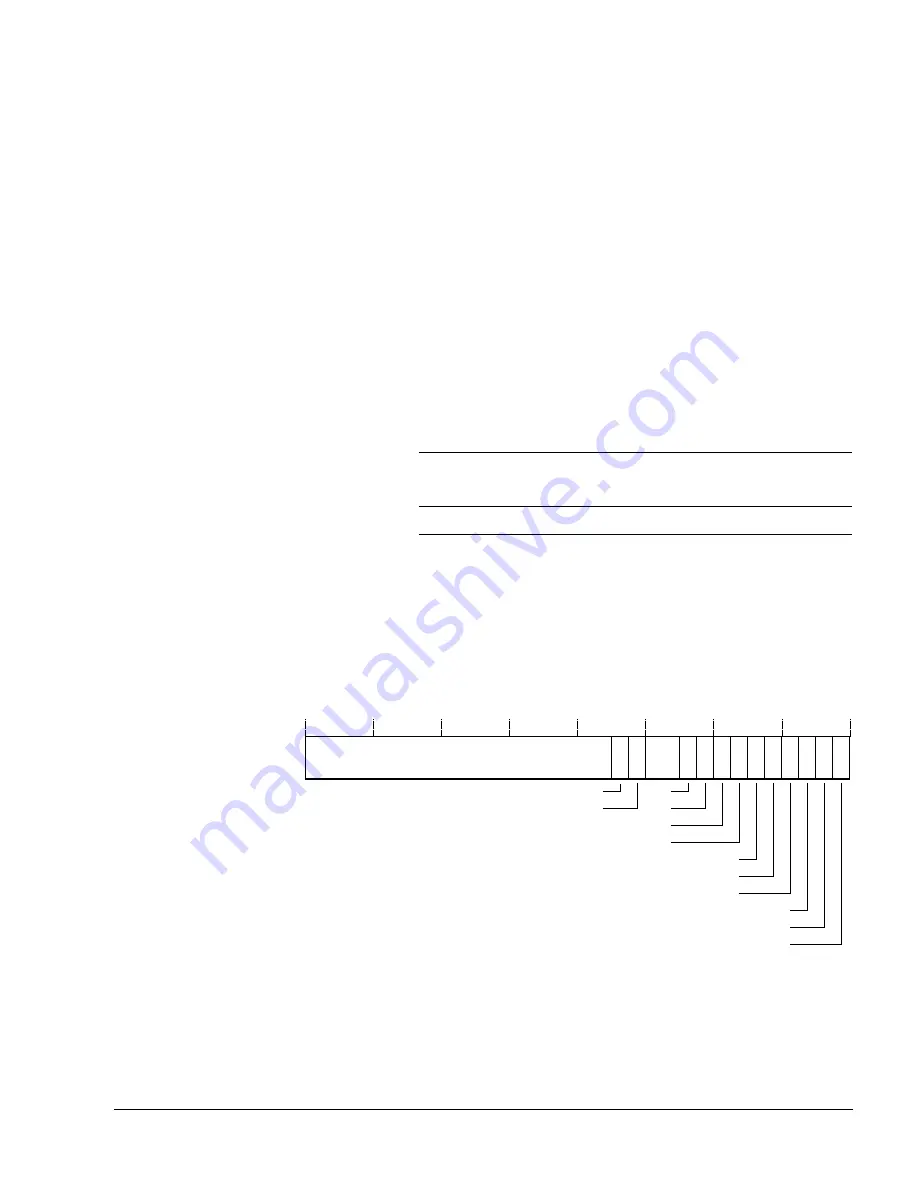

Figure 4-101

shows the SCR bit assignments.

Figure 4-101 SCR bit assignments

b. If the cp11 and cp10 fields are set to different values, the behavior is the same as if both fields were set to the value of cp10, in all respects

other than the value read back by explicitly reading cp11.

EL0

NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

-

RW

-

RW

RW

31

10 9 8 7 6

4 3 2 1 0

RES

0

SIF

HCE

FIQ

IRQ

NS

TWI

TWE

11

12

13

14

SCD

5

nET

EA

FW

AW

RES

0