System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-239

ID021414

Non-Confidential

4.5.47

Hyp Auxiliary Configuration Register

The processor does not implement HACR, so this register is always

RES

0.

4.5.48

Data Fault Status Register

The DFSR characteristics are:

Purpose

Holds status information about the last data fault.

Usage constraints

This register is accessible as follows:

Configurations

DFSR (NS) is architecturally mapped to AArch64 register ESR_EL1.

There are separate Secure and Non-secure copies of this register.

There are two formats for this register. The current translation table format

determines which format of the register is used.

Attributes

DFSR is a 32-bit register.

This section describes:

•

DFSR when using the Short-descriptor translation table format

.

•

DFSR when using the Long-descriptor translation table format

on page 4-241

.

DFSR when using the Short-descriptor translation table format

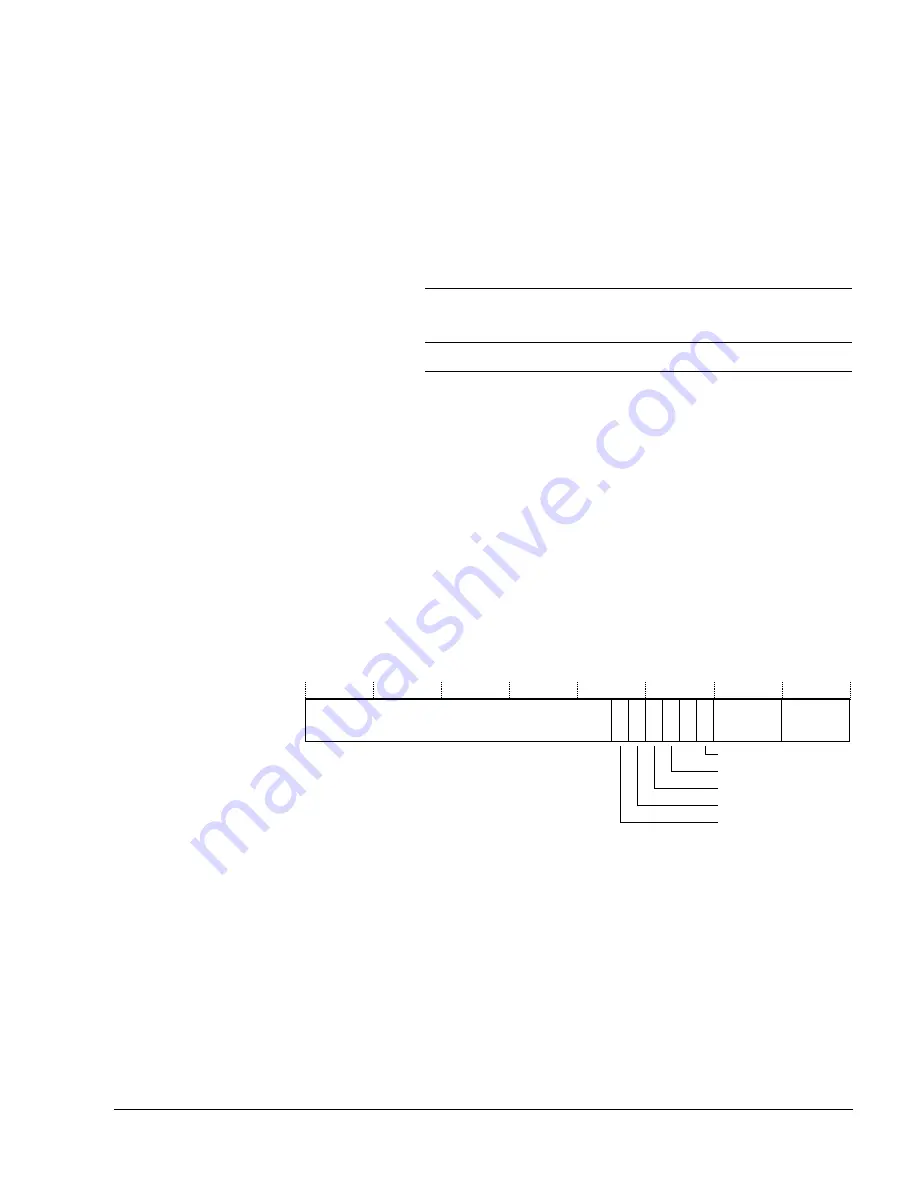

Figure 4-121

shows the DFSR bit assignments when using the Short-descriptor translation table

format.

Figure 4-121 DFSR bit assignments for Short-descriptor translation table format

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW

RW

RW

RW

31

14 13 12 11 10 9 8 7

4 3

0

RES

0

0

CM

ExT

WnR

FS[4]

RES

0

Domain

FS[3:0]