Performance Monitor Unit

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

12-3

ID021414

Non-Confidential

12.2

PMU functional description

This section describes the functionality of the PMU in:

•

Event interface

.

•

System register and APB interface

.

•

Counters

.

•

PMU register interfaces

.

•

External register access permissions

on page 12-4

.

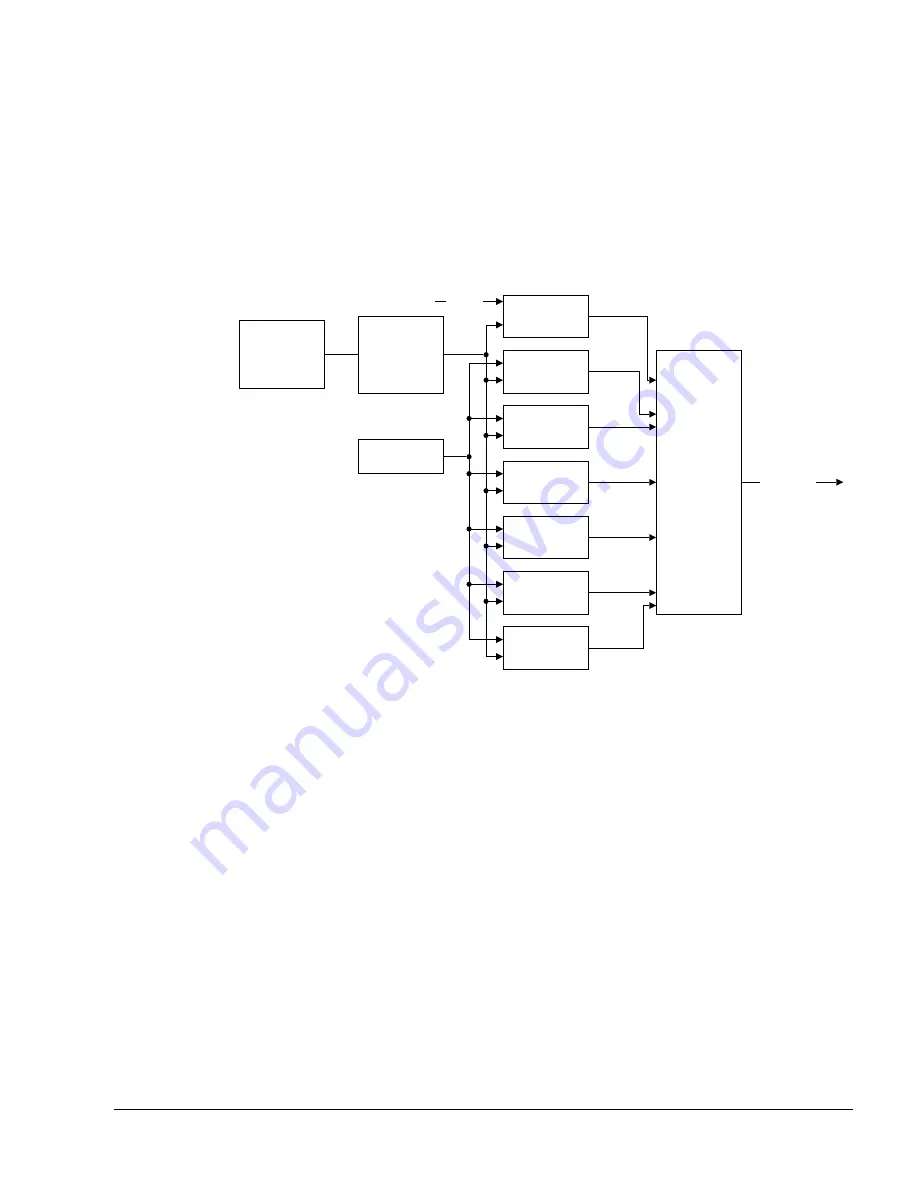

Figure 12-1

shows the various major blocks inside the PMU.

Figure 12-1 PMU block diagram

12.2.1

Event interface

Events from all other units from across the design are provided to the PMU.

12.2.2

System register and APB interface

You can program the PMU registers using the system registers or external APB interface.

12.2.3

Counters

The PMU has 32-bit counters that increment when they are enabled based on events and a 64-bit

cycle counter.

12.2.4

PMU register interfaces

The Cortex-A53 processor supports access to the performance monitor registers from the

internal system register interface and a memory-mapped interface. External access to the

performance monitor registers is also provided with the APB slave port. See

External debug

interface

on page 11-37

.

Cycle Counter

Performance

Counter

Performance

Counter

Count Enable

Set/Clear

Event

Selection

Registers

CLKIN

Events from

other units

nPMUIRQ

System

Control

Processor/

APB interface

Interrupt/

Overflow

registers

Performance

Counter

Performance

Counter

Performance

Counter

Performance

Counter