System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-269

ID021414

Non-Confidential

4.5.76

CPU Auxiliary Control Register

The CPUACTLR characteristics are:

Purpose

Provides

IMPLEMENTATION

DEFINED

configuration and control options for

the processor. There is one 64-bit CPU Auxiliary Control Register for each

core in the cluster.

Usage constraints

This register is accessible as follows:

The CPU Auxiliary Control Register can be written only when the system

is idle. ARM recommends that you write to this register after a powerup

reset, before the MMU is enabled, and before any ACE or ACP traffic

begins.

Note

Setting many of these bits can cause significantly lower performance on

your code. Therefore, it is suggested that you do not modify this register

unless directed by ARM.

Configurations

CPUACTLR is:

•

Common to the Secure and Non-secure states.

•

Mapped to the AArch64 CPUACTLR_EL1 register. See

CPU

Auxiliary Control Register, EL1

on page 4-124

.

Attributes

CPUACTLR is a 64-bit register.

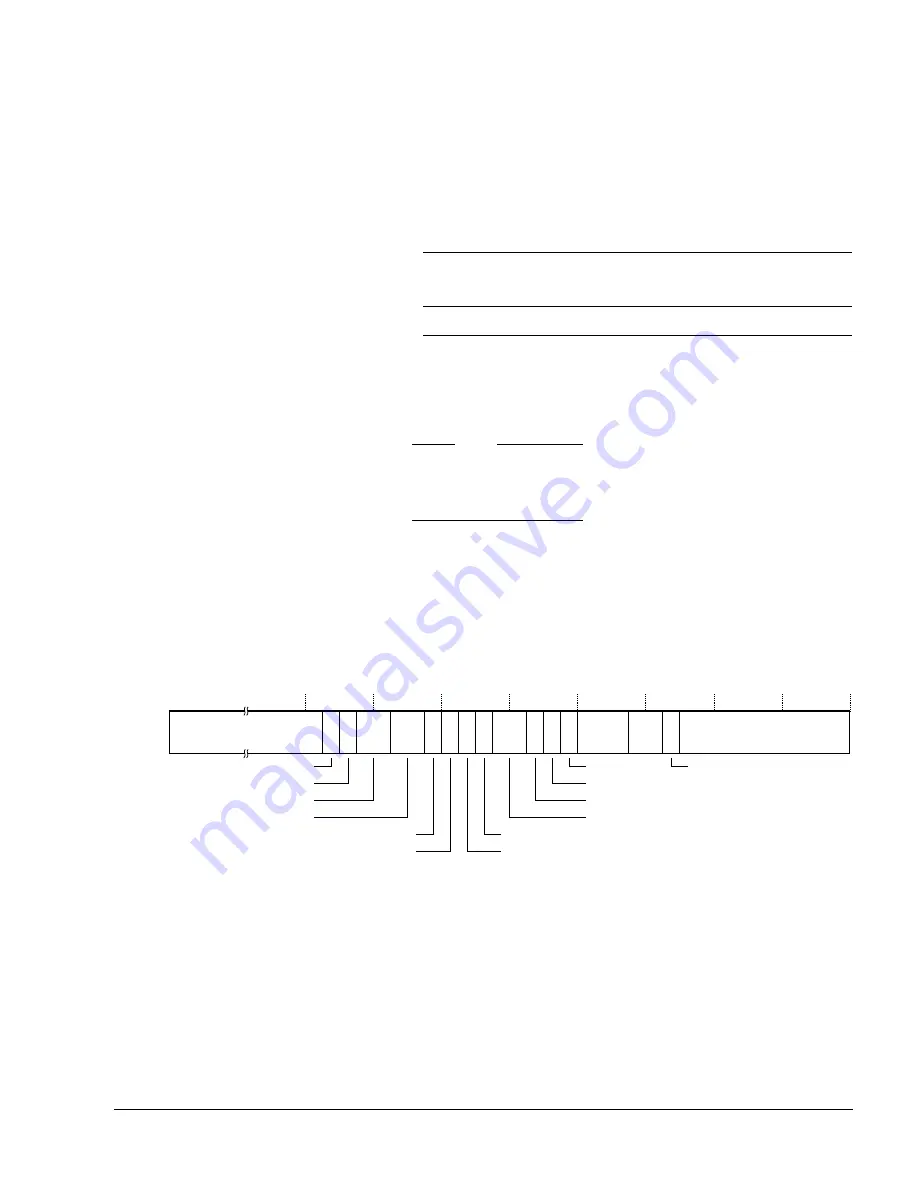

Figure 4-140

shows the CPUACTLR bit assignments.

Figure 4-140 CPUACTLR bit assignments

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW

RW

RW

RW

31

22

18 17

0

9

10

11

12

13

15

16

19

20

21

28

29

RES

0

DIDIS

RES

0

L1PCTL

L1RADIS

RADIS

DODMBS

RES

0

IFUTHDIS

NPFSTRM

DSTDIS

STRIDE

63

FPDIDIS

30

23

24

STBPFDIS

STBPFRS

27 26 25

DTAH

RES

0